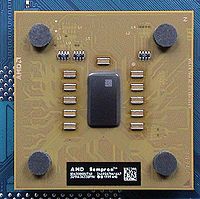

- AMD Sempron

-

Sempron

Microprocesador

Sempron 3000+, Socket-AProducción Desde julio de 2004 Fabricante(s) AMD Frecuencia de reloj de CPU 1 GHz a 2,9 GHz Velocidad de FSB 166 MHz a 200 MHz Conjunto de instrucciones x86, AMD64 Zócalo(s) Socket A

Socket 754

Socket 939

Socket AM2

Socket AM3Núcleo(s) Thoroughbred B/Thorton

Barton

Paris

Palermo (Socket 754, 939)

Manila (Socket AM2)El Sempron es una categoría de microprocesador de bajo costo con arquitectura X86 fabricado por AMD. El AMD Sempron reemplaza al procesador Duron siendo su principal competidor el procesador Celeron de Intel. Las primeras versiones fueron lanzadas al mercado en agosto de 2004.

Las versiones iniciales de este procesador estaban basadas en el núcleo Thoroughbred/Thorton del Athlon XP, con una caché de segundo nivel de 256 KiB y un bus de 333 MHz (FSB 166 MHz). Su índice de prestaciones relativas (PR) se situaba entre 2400+ y 2800+ dependiendo del modelo, aunque el índice no es calculado de la misma forma que para los Athlon XP, siendo los Sempron algo más lentos a mismo índice de prestaciones relativas.

Posteriormente el Sempron se basó en el núcleo Barton del Athlon XP. Esta versión tenía un índice de prestaciones relativas de 3000+ y poseía una caché de segundo nivel de 512 KiB. Las versiones del Sempron basadas en el Athlon XP se puede emplear en placas base con zócalo de procesador Socket A.

En el transcurso de tiempo en que se agotaron las versiones basadas en los núcleos Barton y Thoroughbred/Thorton, estas fueron reemplazadas con una variante del núcleo del Athlon 64 llamada Paris, que no implementa el conjunto de instrucciones AMD64, pero sí el controlador de memoria, con una caché de segundo nivel de 256 KiB. Estas versiones del Sempron se puede emplear en placas base con zócalo de procesador Socket 754.

Desde hace algunos años todos los procesadores Sempron que se comercializan lo hacen con el conjunto de instrucciones AMD64 activado, basadas en el núcleo Palermo, que incorpora soporte parcial para instrucciones SSE3, y puede venir con una caché de segundo nivel de 128 o 256 KiB, dependiendo de sus prestaciones relativas, que tienen tope en el modelo 3800+ dentro del nuevo zócalo AM2.

Contenido

Modelos para Socket A (Socket 462)

Thoroughbred B/Thorton (130 nm)

- caché L1: 128 KiB (64 KiB para datos y los otros 64 KiB para instrucciones)

- Caché L2: 256 KiB fullspeed (es decir, a la misma velocidad del propio núcleo)

- MMX, 3DNow!, SSE

- Socket A (EV6)

- Velocidad del FSB: 166 MHz (FSB 333 DDR).

- Voltaje en el núcleo (Vcore): 1,6 V

- Lanzamiento: 28 de julio de 2004

- Velocidad del reloj: 1,5-2 GHz (2200+ a 2800+)

Barton (130 nm)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 512 KiB, velocidad total

- MMX, 3DNow!, SSE

- Socket A (EV6)

- Velocidad del FSB: 166 MHz – 200 MHz (FSB 333 – 400)

- VCore: 1,6–1,65 V

- Lanzamiento: 17 de septiembre de 2004

- Velocidad del reloj: 2-2,2 GHz (Sempron 3000+, Sempron 3300+)

Modelos para Socket 754

Paris (130 nm SOI)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 256 KiB

- MMX, 3DNow!, SSE, SSE2

- Enhanced Virus Protection (NX bit)

- Controlador de memoria SDRAM DDR integrado de 72 bits de canal simple (64 bits más 8 adicionales con capacidad de control y corrección del tipo ECC)

- Zócalo Socket 754, 800 MHz HyperTransport

- VCore: 1,4 V

- Anunciado: 28 de julio de 2004

- Velocidad del reloj: 1,8 GHz (3100+)

- Stepping: CG (Part No.: *AX)

Palermo (90 nm SOI)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 128/256 KiB, máxima velocidad

- Caché L2 de 128 KiB (Sempron 2600+, 3000+ y 3300+)

- Caché L2 de 256 KiB (Sempron 2500+, 2800+, 3100+ y 3400+)

- MMX, 3DNow!, SSE, SSE2

- Soporte SSE3 sobre steppings E3 y E6

- Registros y extensiones de 64 bits (AMD64) en el stepping E6

- Cool'n'Quiet (Sempron 3000+ y superiores)

- Enhanced Virus Protection (NX bit)

- Controlador de memoria DDR integrado de 72 bits con control de paridad mediante la técnica ECC)

- Zócalo Socket 754, 800 MHz HyperTransport

- VCore: 1,4 V

- Anunciado: Febrero de 2005

- Velocidad de reloj: 1,4-2 GHz

- Steppings: D0 (Part No.: *BA), E3 (Part number: *BO), E6 (Part No.: *BX)

Modelos para Socket 939

Palermo (90 nm SOI)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 128/256 KiB, máxima velocidad

- Caché L2 de 128 KiB (Sempron 3000+ y 3400+)

- Caché L2 de 256 KiB (Sempron 3200+ y 3500+)

- MMX, 3DNow!, SSE, SSE2, SSE3, AMD64 (Sólo en el stepping), Cool'n'Quiet, bit NX

- Controlador de memoria DDR integrado de 144 bits (128 bits para datos y los otros 16 para ECC)

- Socket 939, 800 MHz HyperTransport

- VCore: 1,35/1,4 V

- Lanzamiento: Octubre de 2005

- Velocidad de reloj: 1,8-2 GHz

- Steppings: E3 (Part No.: *BP), E6 (Part No.: *BW)

Modelos para Socket AM2

Manila (90 nm SOI)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 128/256 KiB, máxima velocidad

- Caché L2 de 128 KiB (Sempron 2800+, 3200+ y 3500+)

- Caché L2 de 256 KiB (Sempron 3000+, 3400+, 3600+ y 3800+)

- MMX, Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, bit NX

- Controlador de memoria DDRSDRAM de 128 bits integrado

- Controlador de memoria DDR2 integrado de 128 bits (Doble canal)

- Socket AM2, 800 MHz HyperTransport

- VCore: 1,25/1,35/1,40 V (1,20/1,25 V para Eficientes SFF version)

- Lanzamiento: 23 de mayo de 2006

- Velocidad de reloj: 1,6-2,2 GHz

- Stepping: F2 (Part No.: *CN, *CW)

Sparta (65 nm SOI)

- Caché L1: 64 + 64 KiB (Datos + instrucciones)

- Caché L2: 256/512 KiB, máxima velocidad

- Caché L2 de 256 KiB (Sempron LE-1100, LE-1150)

- Caché L2 de 512 KiB (Sempron LE-1200, LE-1250, LE-1300)

- MMX, Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, bit NX

- Controlador de memoria DDR2 integrado de 128 bits (Doble canal)

- Socket AM2, 800 MHz HyperTransport

- VCore: 1,20/1,40 V

- Lanzamiento: 20 de agosto de 2007

- Velocidad del reloj: 1,9-2,3 GHz

- Stepping: G1 (Part No.: *DE), G2 (Part No.: *DP)

Modelos para Socket AM3

Sargas (45 nm SOI)

- Velocidad del núcleo: 2,7 GHz

- Temperatura máxima (C): 65

- Vatiaje: 45 W

- Caché L1 (KiB): 128

- Caché L2 (KiB): 1.024

- Arquitectura de CPU: 1 CPU - 1 núcleo - 1 hebra

- MMX(+), 3DNow! (+), SSE, SSE2 SSE3, SSE4A, x86-64, AMD-V, Cool'n'Quiet, bit NX

- CPUID: F.6,2 / Extended : 10,6

- Núcleo: (45 nm) / Stepping : BL-C2

Modelos para Socket S1 (638)

Keene (90 nm SOI)

- Caché L1: 64 + 64 KiB (Datos + instrucciones)

- Caché L2: 256 ó 512 KiB, máxima velocidad

- Caché L2 de 256 KiB (Sempron 2100+ y 3400+)

- Caché L2 de 512 KiB (Sempron 3200+, 3500+ y 3600+)

- MMX, Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, bit NX

- Controlador de memoria de 128 bits (de doble canal) DDR2 integrado

- Socket S1, 800 MHz HyperTransport

- VCore: 0,95-1,25 V

- Lanzamiento: 17 de mayo de 2006

- Velocidad del reloj: 1-2 GHz

- Stepping: F2 (Part No.: *CM)

Sable (65 nm SOI)

- memoria cache|Caché]] L1: 64 + 64 KiB (Datos + instrucciones)

- Caché L2: 512 KiB, máxima velocidad

- MMX, Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, bit NX

- Controlador de memoria de 128 bits (de doble canal) DDR2 integrado

- Socket S1, 1.600 MHz HyperTransport

- VCore: 0,950-1,25 V

- Lanzamiento: 8 de enero de 2009

- Velocidad del reloj: 2-2,1 GHz

Modelos para ASB1 package (BGA)

Huron (65 nm SOI)

- Caché L1: 64 + 64 KiB (Datos e instrucciones)

- Caché L2: 256 KiB, máxima velocidad

- MMX, Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, bit NX

- Controlador de memoria de 128 bits (de doble canal) DDR2 integrado

- Empaque ASB1, 800 MHz HyperTransport

- VCore: ?

- Lanzamiento: 8 de enero de 2009

- Velocidad del reloj: De 1 a 1,5 GHz

- Caché L2 de 256 KiB

- TDP:

- Sempron 200U: 8 W

- Sempron 210U: 15 W

- Stepping: ? (Part No.: *DV)

Categoría:- Microprocesadores AMD

Wikimedia foundation. 2010.