- Coherencia de caché

-

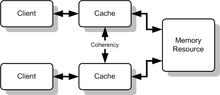

La coherencia de cache hace referencia a la integridad de los datos almacenados en las caches locales de los recursos compartidos. La coherencia de la cache es un caso especial de la coherencia de memoria.

Cuando los clientes de un sistema, en particular las CPUs en un multiprocesador, mantienen caches de una memoria compartida, los conflictos crecen. Haciendo referencia al dibujo, si el cliente de arriba tiene una copia de un bloque de memoria de una lectura previa y el cliente de abajo cambia ese bloque, el cliente de arriba podría estar trabajando con datos erróneos, sin tener conocimiento de ello. La coherencia de la cache intenta administrar estos conflictos y mantener consistencia entre las caches y la memoria.

Mecanismos para la coherencia de la cache

Los protocolos basados en directorio mantienen un directorio centralizado de los bloques que hay en las caches. Se utilizan tanto en multiprocesadores con memoria físicamente distribuida, como en sistemas con memoria centralizada con red escalable. Estos protocolos de mantenimiento de coherencia reducen el tráfico en la red enviando selectivamente órdenes sólo a aquellas caches que disponen de una copia válida del bloque implicado en la operación de memoria.

El protocolo Snoopy hace que las caches individualmente monitoreen las líneas(buses) de direcciones de accesos a memoria con respecto a los bloques que han copiado. Cuando una operación de escritura es observada sobre una dirección de un bloque del cual tiene un bloque, el controlador de cache invalida su copia. También es posible que el controlador de cache observe la dirección y el dato correspondiente a esa dirección, intentando así actualizar su copia cuando alguien modifica dicho bloque en la memoria principal.

El protocolo de memoria distribuida imita a los anteriores en un intento de mantener la consistencia entre bloques de memoria en sistemas con débil acoplamiento.

Modelos de coherencia

Varios modelos y protocolos han sido desarrollados para mantener la coherencia de la cache, tales como protocolo MSI, protocolo MESI, protocolo MOSI y el protocolo MOESI. La elección de un modelo de consistencia es crucial a la hora de diseñar un sistema de cache coherente. Los modelos de coherencia difieren en rendimiento y escalabilidad, por lo que deben ser evaluados para cada sistema diseñado.

Además, las transiciones entre estados en una implementación en concreto de estos protocolos puede variar. Por ejemplo una implementación puede elegir diferentes transiciones para actualizar y actualiza tales como actualización-en-lectura, actualización-en-escritura, invalidación-en-lectura, o invalidación-en-escritura. La elección de una transición puede afectar a la cantidad de tráfico entre caches, lo que a su vez podría afectar al ancho de banda disponible por las caches para la operación actual. Esto debe ser tenido en consideración en el diseño de software distribuido que podría causar problemas de contención entre caches de múltiples procesadores.

Véase también

- Bus sniffing

- Protocolos de coherencia basados en directorio

- NUMA

- Write barrier

Wikimedia foundation. 2010.