- MSP430

-

El MSP430 es una familia de microcontroladores producidos por Texas Instruments. Construido con una CPU de 16 bits, el MSP430 está diseñado para aplicaciones empotradas de bajo costo y bajo consumo de energía. La arquitectura tiene reminiscencias del DEC PDP-11. Desafortunadamente, el MSP430 carece de una característica muy importante del PDP11, la cual era la memoria para indexar memoria. Esta carcterística permitía que las rutinas de interrupción se escribieran sin utilizar registros, por lo que no requería apilamientos. El MSP430 es muy útil para aplicaciones inalámbricas o para aplicaciones de bajo consumo.

Este dispositivo tiene una variedad de configuraciones con los siguientes periféricos: oscilador interno, timer incluyendo un PWM, watchdog, USART, SPI, I2C, 10/12/14/16-bit ADCs, and brownout reset circuitry. Algunos periféricos opcionales no tan usuales incluyen comparadores (que se utilizan con el timer para funcionar como un ADC simple), amplificadores operacionales dentro del chip para el acondicionamiento de señales, DAC de 12 bits, controlador de LCD, hardware multiplier, y DMA para el manejo de salidas del ADC. A diferencia de las versiones anteriores con EPROM (PMS430E3xx) y mask ROM (MSP430Cxxx), estos dispositivos son programables en sistema a través de JTAG o a través del bootstrap loader (BSL) usando RS-232.

Contenido

La CPU del MSP430

La CPU usa una arquitectura von Neumann, con direccionamiento simple para las instrucciones y los datos. La memoria se direcciona por byte, y los pares de byte se combinan en forma endianness para hacer palabras de 16 bits.

El procesador contiene 16 registros de 16 bits. R0 es el contador de programa, R1 es el puntero de pila, R2 es el registro de estado, y R3 es un registro especial denominado generador constante, que provee acceso a 6 valores constantes comúnmente utilizados, sin requerir un operando adicional. R4 hasta R15 son para uso general.

El conjunto de instrucciones es muy simple; hay 27 instrucciones agrupadas en tres familias. La mayoría de las instrucciones son de 8 bit (un byte) y 16 bit (palabra), dependiendo del valor de un bit llamado B/W, este bit es 1 para instrucciones de 8 bits y 0 para las de 16 bits. Las operaciones de byte sobre la memoria afectan solo al byte direccionado, mientras que las operaciones de byte sobre los registros al byte más significativo.

Conjunto de instrucciones del MSP430 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Instrucción 0 0 0 1 0 0 opcode B/W As register Single-operand arithmetic 0 0 0 1 0 0 0 0 0 B/W As register RRC Rotate right through carry 0 0 0 1 0 0 0 0 1 0 As register SWPB Swap bytes 0 0 0 1 0 0 0 1 0 B/W As register RRA Rotate right arithmetic 0 0 0 1 0 0 0 1 1 0 As register SXT Sign extend byte to word 0 0 0 1 0 0 1 0 0 B/W As register PUSH Push value onto stack 0 0 0 1 0 0 1 0 1 0 As register CALL Subroutine call; push PC and move source to PC 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 0 RETI Return from interrupt; pop SR then pop PC 0 0 1 condition 10-bit signed offset Conditional jump; PC = PC + 2×offset 0 0 1 0 0 0 10-bit signed offset JNE/JNZ Jump if not equal/zero 0 0 1 0 0 1 10-bit signed offset JEQ/JZ Jump if equal/zero 0 0 1 0 1 0 10-bit signed offset JNC/JLO Jump if no carry/lower 0 0 1 0 1 1 10-bit signed offset JC/JHS Jump if carry/higher or same 0 0 1 1 0 0 10-bit signed offset JN Jump if negative 0 0 1 1 0 1 10-bit signed offset JGE Jump if greater or equal 0 0 1 1 1 0 10-bit signed offset JL Jump if less 0 0 1 1 1 1 10-bit signed offset JMP Jump (unconditionally) opcode source Ad B/W As destination Two-operand arithmetic 0 1 0 0 source Ad B/W As destination MOV Move source to destination 0 1 0 1 source Ad B/W As destination ADD Add source to destination 0 1 1 0 source Ad B/W As destination ADDC Add source and carry to destination 0 1 1 1 source Ad B/W As destination SUBC Subtract source from destination (with carry) 1 0 0 0 source Ad B/W As destination SUB Subtract source from destination 1 0 0 1 source Ad B/W As destination CMP Compare (pretend to subtract) source from destination 1 0 1 0 source Ad B/W As destination DADD Decimal add source to destination (with carry) 1 0 1 1 source Ad B/W As destination BIT Test bits of source AND destination 1 1 0 0 source Ad B/W As destination BIC Bit clear (dest &= ~src) 1 1 0 1 source Ad B/W As destination BIS Bit set (logical OR) 1 1 1 0 source Ad B/W As destination XOR Exclusive or source with destination 1 1 1 1 source Ad B/W As destination AND Logical AND source with destination (dest &= src) NdT: "Palabra de extensión" es la traducción de "Extension Word"

Las instrucciones son 16 bits, seguidas de hasta dos palabras de extensión de 16 bits. Hay cuatro modos de direccionamiento, especificados por el bit 2 como campo. Algunas versiones especiales pueden ser construidas usando R0, y otros modos a parte del acceso directo al registro usando R2 (el registro de estado) y R3 (el generador constante) son interpretados especialmente.

Los modos de direccionamiento indexado añaden una palabra de extensión de 16 bits a la instrucción.

Modos de direccionamiento del MSP430 As Register Syntax Description 00 n Rn Register direct. The operand is the contents of Rn. 01 n x(Rn) Indexed. The operand is in memory at address Rn+x. 10 n @Rn Register indirect. The operand is in memory at the address held in Rn. 11 n @Rn+ Indirect autoincrement. As above, then the register is incremented by 1 or 2. Addressing modes using R0 (PC) 01 0 (PC) LABEL Symbolic. x(PC) The operand is in memory at address PC+x. 11 0 (PC) #x Immediate. @PC+ The operand is the next word in the instruction stream. Addressing modes using R2 (SP) and R3 (CG), special-case decoding 01 2 (SR) &LABEL Absolute. The operand is in memory at address x. 10 2 (SR) #4 Constant. The operand is the constant 4. 11 2 (SR) #8 Constant. The operand is the constant 8. 00 3 (CG) #0 Constant. The operand is the constant 0. 01 3 (CG) #1 Constant. The operand is the constant 1. There is no index word. 10 3 (CG) #2 Constant. The operand is the constant 2. 11 3 (CG) #-1 Constant. The operand is the constant -1. Las instrucciones generalmente consumen un ciclo (de reloj) por palabra adquirida o almacenada, por lo que la duración de las instrucciones va desde 1 ciclo para instrucciones de registro a registro a 6 ciclos para una instrucción con los dos operandos indexados.

Operaciones de transferencia (Moves) al contador de programa son legales y conllevan saltos. Los retornos de una subrutina por ejemplo, se implementan así: MOV @SP+,PC. En instrucciones con dos operandos, solo hay un bit "Ad" para especificar el modo de direccionamiento del destino, por lo que solo los modos 00 (directamente a registro) y 01 (indexado) están permitidos. Si tanto el origen como el destino son indexados, la palabra de extensión del origen va primero.

Cuando R0 (PC) o (R1) SP son unsados con el modo de acceso de autoincremeto, siempre son incrementados en dos. Otros registros (desde R4 a R15) son incrementados en el tamaño del operador, 1 o 2 bytes.

El registro de estado contiene cuatro bits de estado aritmético, una tabla de interrupciones global, y 4 bits que desabilitan varios relojes para entrar en modo de bajo consumo. Cuando se atiende una interrupción, el procesador almacena el registro de estado en la pila y limpia los bits de bajo consumo. Si el vector de interrupción no modifica el registro de estado almacenado, volver de la interrupción, rehabilitara el modo de bajo consumo que estuviese habilitado previamente.

Mapa de direcciones del MSP430

La disposicion general de las direcciones del MSP430 es:

- 0x0000–0x0007

- Resgistros para funciones especiales del procesador(Registro para el control de interrupciones)

- 0x0008–0x00FF

- Perifericos de 8-bit. Se debe acceder a estos utilizando 8 bits para lectura-escritura.

- 0x0100–0x01FF

- Perifericos de 16-bit. Se debe acceder a estos utilizando 16 bits para lectura-escritura.

- 0x0200–0x09FF

- Hasta 2048 bytes de Memoria RAM.

- 0x0C00–0x0FFF

- 1024 bytes de bootstrap loader ROM (para las versiones que incluyen flash ROM).

- 0x1000-0x1100

- 256 bytes de data flash ROM (para las versiones que incluyen flash ROM).

- 0x1100–0x38FF

- Extension de RAM para modelos de mas de 2048 bytes de RAM. (0x1100–0x18FF es una copia de 0x0200–0x09FF)

- 0x1100–0xFFFF

- Hasta 60 kilobytes de ROM de programa. el inicio de modelos con ROM mas pequena comienzan en direcciones superiores. Los ultimos 16 o 32 bytes son para el vector de interrupcion.

Algunos modelos incluyen mas the 2048 bytes de RAM; en ese caso la RAM comienza en 0x1100 los primeros 2048 bytes (0x1100–0x18FF) son llevados al intervalo 0x0200–0x09FF para cuestiones de compatibilidad. además, algunos modelos recientes unen las reglas para perifericos de 8 y 16 bits, permitiendo el uso de perifericos de 16-bit en el rango de direcciones de perifericos de 8 bits.

Existe una nueva version extendida de esta arquitectura (llamada MSP430X) que permite el uso de un espacio de direcciones de 20 bit. Esto permite iniciar la ROM en la direccion 0x10000.

Familias del MSP430

Existen cuatro familias principales del procesador MSP430. En orden de desarrollo, fueron: La familia '3xx, la familia '1xx, la familia '4xx, y la familia '2xx. Los dígitos después de la letra de familia, identifican el modelo (generalmente un número mayor representa un modelo mas potente), el tercer dígito indica la cantidad de memoria integrada, y el cuarto -si es que existe-, identifica una variante mínima del modelo.

- MSP430x1xx

- Es la famila básica sin pantalla LCD integrada. Son normalmente mas pequeños que el de la familia '3xx.

- MSP430F2xx

- Es similar a la familia '1xx, pero opera con aún menor consumo, soporta velocidades de operación de hasta 16Mhz (las otras familias estan limitadas a 8Mhz), y son mas precisas (+/- 2%) en la sincronía del reloj, lo que los hace mas fáciles de operar sin un cristal externo.

- MSP430x3xx

- Es la familia mas antigua de esta serie de microcontroladores. Fué diseñada para instrumentos portátiles con pantalla LCD integrada. Incluye un oscilador [frequency-locked loop] que puede sincronizarlo automáticamente con cristales de baja velocidad (32Khz). Esta familia no soporta memorias EEPROM, solamente ROM y EPROM. Familias posteriores proveyeron solamente soporte Flash y ROM.

- MSP430x4xx

- Esta familia es muy similar a la '3xx, también incluye un controlador LCD, pero es mejor y más capaz, y viene en versiones de máscara o flash ROM.

Periféricos

The MSP430 peripherals are generally easy to use, with (mostly) consistent addresses between models, and no write-only registers.

Puertos de entrada-salida (E/S) de propósito general

As is standard on microcontrollers, most pins connect to a more specialized peripheral, but if that peripheral is not needed, the pin may be used for general-purpose I/O. The pins are divided into 8-bit groups called "ports", each of which is controlled by a number of 8-bit registers.

The MSP430 family defines 11 I/O ports, P0 through P10, although no chip implements more than 10 of them. P0 is only implemented on the '3xx family. P7 through P10 are only implemented on the largest members of the '4xx family.

- PxIN

- Port x input. This is a read-only register, and reflects the current state of the pin.

- PxOUT

- Port x output. The values written to this read/write register are driven out the corresponding pins when they are configured to output.

- PxDIR

- Port x data direction. Bits written as 1 configure the corresponding pin for output. Bits written as 0 configure the pin for input.

- PxSEL

- Port x function select. Bits written as 1 configure the corresponding pin for use by the specialized peripheral. Bits written as 0 configure the pin for general-purpose I/O. Port 0 ('3xx parts only) is not multiplexed with other peripherals and does not have a P0SEL register.

- PxREN

- Port x resistor enable ('2xx only). Bits set in this register enable weak pull-up or pull-down resistors on the corresponding I/O pins even when they are configured as inputs. The direction of the pull is set by the bit written to the PxOUT register.

- PxIES

- Port x interrupt edge select (ports 0-2 only). Selects the edge which will cause the PxIFG bit to be set. When the input bit changes from matching the PxIES state to not matching it (i.e. whenever a bit in PxIES XOR PxIN changes from clear to set), the corresponding PxIFG bit is set.

- PxIFG

- Port x interrupt flag (ports 0-2 only). Set whenever the corresponding pin makes the state change requested by PxIES. Can be cleared only by software. (Can also be set by software.)

- PxIE

- Port x interrupt enable (ports 0-2 only). When this bit and the corresponding PxIFG bit are both set, an interrupt is generated.

Note that some pins have special purposes either as inputs or outputs. (For example, timer pins can be configured as capture inputs or PWM outputs.) In this case, the PxDIR bit controls which of the two functions the pin performs even when the PxSEL bit is set. If there is only one special function, then PxDIR is generally ignored.

The PxIN register is still readable if the PxSEL bit is set, but interrupt generation is disabled. If PxSEL is clear, the special function's input is frozen and disconnected from the external pin. Also, configuring a pin for general-purpose output does not disable interrupt generation.

General-purpose I/O register address map PxIN PxOUT PxDIR PxSEL PxIES PxIE PxIFG PxREN P0 0x10 0x11 0x12 0x13 0x14 0x15 P1 0x20 0x21 0x22 0x23 0x24 0x25 0x26 0x27 P2 0x28 0x29 0x2a 0x2b 0x2c 0x2d 0x2e 0x2f P3 0x18 0x19 0x1a 0x1b 0x10 P4 0x1c 0x1d 0x1e 0x1f 0x11 P5 0x30 0x31 0x32 0x33 0x12 P6 0x34 0x35 0x36 0x37 0x13 P7 0x38 0x3a 0x3c 0x3e P8 0x39 0x3b 0x3d 0x3f P9 0x08 0x0a 0x0c 0x0e P10 0x09 0x0b 0x0d 0x0f Ports P7 and P8 may be accessed using 16-bit loads and stores; when used this way, the combination is known as PA. Similarly, P9 and P10 bay be combined into a 16-bit PB.

Multiplicador por hardware

Some MSP430 models include a memory-mapped hardware multiplier peripheral which performs various 16×16+32→33-bit multiply-accumulate operations.

Unusually for the MSP430, this peripheral does include an implicit 2-bit write-only register, which makes it effectively impossible to context switch.

The 8 registers used are:

Address Name Function 0x130 MPY Operand1 for unsigned multiply 0x132 MPYS Operand1 for signed multiply 0x134 MAC Operand1 for unsigned multiply-accumulate 0x136 MACS Operand1 for signed multiply-accumulate 0x138 OP2 Second operand for multiply operation 0x13a ResLo Low word of multiply result 0x13c ResHi High word of multiply result 0x13e SumExt Carry out of multiply-accumulate The first operand is written to one of four 16-bit registers. The address written determines the operation performed. While the value written can be read back from any of the registers, the register number written to cannot be recovered.

If a multiply-accumulate operation is desired, the

ResLoandResHiregisters must also be initialized.Then, each time a write is performed to the

OP2register, a multiply is performed and the result stored or added to the result registers. TheSumExtregister is a read-only register that contains the carry out of the addition (0 or 1) in case of an unsigned multiply), or the sign extension of the 32-bit sum (0 or -1) in case of a signed multiply. In the case of a signed multiply-accumulate, theSumExtvalue must be combined with the most significant bit of the priorSumHicontents to determine the true carry out result (-1, 0, or +1).The result is available after three clock cycles of delay, which is the time required to fetch a following instruction and a following index word. Thus, the delay is typically invisible. An explicit delay is only required if using an indirect addressing mode to fetch the result.

Herramientas de desarrollo

[inglés] Texas Instruments provides software development tools that can be downloaded for free. The TI-provided toolchain is a Kickstart edition of the IAR C/C++ compiler, which is limited to 4K of C/C++ code in the compiler and debugger (assembly language programs of any size can be developed and debugged with this free toolchain). TI also provides a version of Eclipse that it calls Code Composer Essentials, for which the Kickstart version can be downloaded for free. The open source community produces a freely available software development toolset (MSPGCC) based on the GNU toolset, although the object code size and speed are not as optimal as the results from a commercial compiler.[cita requerida] Also various commercial development toolsets, which include editor, compiler, linker, assembler, debugger and in single cases code wizards, are available. VisSim, a block diagram language for model based development, can generate efficient fixed point C-Code directly from the diagram. By clever use of inline interrupt functions, VisSim generates very efficient control programs that can access I2C, ADC, PWM etc, in a control loop and use less than 1K flash and 128 bytes RAM.

[español: revisar] Texas Instruments provee herramientas de desarrollo de software que pueden ser descargadas gratuitamente. El toolchain provisto por TI en la edición Kickstart del compilador C/C++ IAR, el cual está limitado a 4K de código C/C++ en el compilador y depurador (programas en lenguaje ensamblador de cualquier tamaño pueden ser desarrollados y depurados con este toolchain gratuito). TI adema provee una versión de Eclipse que llama "Code Composer Essentials", para la cual la versión "Kickstart" puede ser descargada gratuitamente. La comunidad del código abierto produce un software de desarrollo "toolset" gratuitamente disponible (MSPGCC) basado en el GNU toolset, aunque el tamaño de tal código y su rapidez no son tan óptimas como los resultados obtenidos por el compilador comercial.[cita requerida] Además varios "toolset" comerciales de desarrollo, los cuales incluyen editor, compilador, "linker", ensamblador, depurador y en casos singulares asistentes de código, están disponibles. VisSim, un lenguaje de diagrama de bloques para desarrollo basado en modelos, puede generar eficiente código-C de punto fijo directamente desde el diagrama. Para un uso inteligente de funciones "inline interrupt", VisSim genera programas de control muy eficientes que pueden acceder a I2C, ADC, PWM etc, en un control de ciclo y usan menos de 1K flash y 128 bytes RAM.

Plataformas de desarrollo

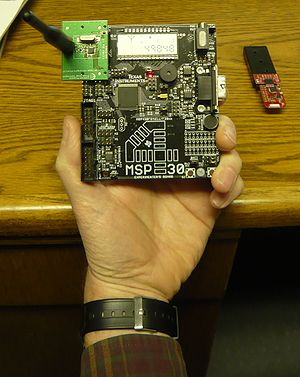

The MSP430 has generated excitement with the availability of inexpensive development platforms. At a cost of $20 USD, TI has packaged a USB stick programmer, the eZ430-F2013, containing an MSP430F2013 on a detachable prototyping board, and CD with development software. This is helpful for schools, hobbyists and garage inventors. It is also welcomed by engineers in large companies prototyping projects with capital budget problems.

One other interesting thing about the MSP430F2013 and its siblings is that it is the only MSP430 part that is available in a dual in-line package (DIP). Other variants in this family are only available in various surface-mount packages. It is clear that TI has gone to some trouble to support the eZ430 development platform by making the raw chips easily prototypable by hobbyists.

While software development using Linux and other Open Source is possible, support from TI is non-existent, and tool support for new processors is untimely late since they rely on volunteers.Interfaz de debug

In common with other microcontroller vendors, TI has developed a two-wire debugging interface found on all their MSP430 parts that replaces the larger JTAG interface. The eZ430 Development Tool contains a full USB-connected Flash Emulation Tool ("FET") for this new two-wire protocol, named "Spy-Bi-Wire" by TI. Spy-Bi-Wire is currently only available on the MSP430F20xx, MSP430F22x2, and MSP430F22x2 devices.

The advantage of the Spy-Bi-Wire protocol is that it uses only two communication lines, one of which is the dedicated _RESET line. The JTAG interface on the lower pin count MSP430 parts is multiplexed with general purpose I/O lines. This makes it relatively difficult to debug circuits built around the small, low-I/O-budget chips, since the full 4-pin JTAG hardware will conflict with anything else connected to those I/O lines. This problem is alleviated with the Spy-Bi-Wire-capable chips, which are still compatible with the normal JTAG interface for backwards compatibility with the old development tools.

JTAG debugging and flash programming tools based on OpenOCD and widely used in the ARM community are not available for the MSP430. Programming tools specially designed for the MSP430 are marginally less expensive than JTAG interfaces that use OpenOCD. However, should a project discover midstream that more MIPS, more memory, and more I/O peripherals are needed, those tools will not transfer to a processor from another vendor.

Enlaces externos

Sitios de información

- TI MSP430 Homepage

- MSP430 Community sponsored by Texas Instruments

- MSP430@UBI group with MSP430 projects, forum and blog

- MSP430.info

- msp430 Yahoo!group

- MSP430web

- MSP430 JTAG at [1]

- MSP430 English-Japanese forum

- MS430 en español. Una guía de referencia Publicación de Arte en 8 bits donde se hace referencia a los principales componentes del popular microcontrolador de Texas Instruments

Generadores de codigo en C visuales

Compiladores y ensambladores

Categoría:- Microcontroladores

Wikimedia foundation. 2010.