- Intel 8259

-

Controlador programable de interrupciones Intel 8259

Controlador programable de interrupciones Intel 8259

El Intel 8259 o PIC 8259 es un controlador programable de interrupciones (PIC), diseñado para ser usando en un sistema que incorpore un microprocesador 8085 u 8086. Un posterior sufijo "A" fue compatible con los procesadores Intel 8086 y 8088. El 8259 combina múltiples entradas de interrupción en una simple salida de interrupción hacia el microprocesador, extendiendo los niveles de interrupción disponibles en un sistema más allá de los uno o dos niveles encontrados en el chip del procesador. El 8259A fue el controlador de interrupciones para el bus ISA en el IBM PC original y el IBM AT.

Contenido

Historia

El 8259 fue introducido como parte de la familia Intel MCS 85 en 1976. El 8259A fue incluido en el PC original en 1981 y mantenido por el IBM XT cuando se introdujo en 1983. Un segundo 8259A fue añadido con la introducción del IBM AT. El 8259A ha coexistido con la arquitectura APIC de Intel, desde su introducción en los PC demultiprocesador simétrico. Los PC modernos ya han comenzado a eliminar por completo el uso del 8259A en favor del uso exclusivo de la arquitectura APIC de Intel. Sin embargo, aunque ya no es un chip separado, la interface del 8259A todavía es proporcionada por el chipset Southbridge en las modernas tarjetas x86.

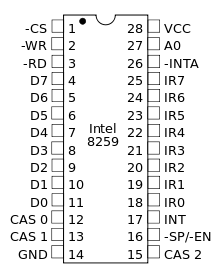

Los conectores principales en un 8259 son los siguientes:

- Ocho líneas de solicitud de interrupción de entrada con el nombre IRQ0 hasta IRQ7

- Una salida de solicitud de interrupción llamada INTR

- Línea de reconocimiento de interrupción llamada INTA

- Líneas de datos de D0 hasta D7 para comunicar el nivel de interrupción o vector de desplazamiento

- Otros conectores incluyen CAS0 hasta CAS2 para cascada entre los 8259.

Hasta ocho 8259 esclavos pueden ser conectados en cascada a un 8259 maestro para proporcionar un máximo de 64 IRQ. Los 8259 son conectados en cascada conectando la línea de INT de un 8259 esclavo a una línea de IRQ de un 8259 maestro.

Hay tres registros internos en el 8259:

- El Interrupt Mask Register (IMR) (Registro de enmascaramiento de interrupción), que mantiene una máscara de las interrupciones actuales pendientes de reconocimiento (acknowledgement)

- El Interrupt Request Register (IRR) (Registro de solicitud de interrupción), que mantiene una máscara de las interrupciones que están pendientes de fin de interrupción (EOI)

- El In-Service Register (ISR) (Registro de En-Servicio), que mantiene una máscara una máscara de interrupciones a las que no se les debe enviar un reconocimiento.

El 8259 soporta los modos de prioridad fijos y rotatorios.

La operaciones de Fin de interrupción (EOI) soportan EOI específico, EOI no específico, y auto-EOI. Un EOI específico indica el nivel de IRQ que está reconociendo en el ISR. Un EOI no específico resetea el nivel de IRQ en el ISR. El auto-EOI resetea el nievl de IRQ en el ISR inmediatamente después de que la interrupción es reconocida.

Los modos de disparo de interrupción de borde y nivel son soportados por el 8259A. Los modos de prioridad fija y prioridad rotativa son soportados.

El 8259 puede ser configurado para trabajar con un 8080/8085 o un 8086/8088. En el 8086/8088, el controlador de interrupciones proporcionará un número de interrupción en el bus de datos cuando se produce una interrupción. El ciclo de interrupción en el 8080/8085 emitirá tres bytes en el bus de datos (que corresponde a una instrucción CALL en el conjunto de instrucciones del 8085).

Estructura del controlador

La estructura del controlador está formada por un conjunto de registros internos que analizaremos a continuación.

- IRR/ISR:: Registro de peticiones de interrupción/Registro de servicio de interrupción. Al activarse una o varias entradas IR quedán reflejadas en los bits correspondientes de IRR. Se usa para decidir a que interrupción atender.

- IMR: Registro de máscaras de interrupción. Se delega la responsabilidad en el programador para enmascarar algunas interrupciones que ayuden al controlador a ignorar dichas interrupciones, aquí cada bit corresponde a una línea IRQ, e indica si esta permitida un interrupción de ese nivel en ese momento.

Consideraciones de Programación

DOS y Windows

La programación de un 8259 en relación con el DOS y Microsoft Windows ha introducido una serie de cuestiones confusas en aras de la compatibilidad hacia atrás, que se extiende tan lejos como el PC original introducido en 1981.

La primera cuestión es más o menos la raíz de la segunda cuestión. Los controladores de dispositivos de DOS que espera para enviar un EOI no específico para el 8259s cuando terminan el servicio de su dispositivo. Esto evita el uso de cualquiera de los otros modos de EOI 8259 en DOS, y excluye la diferenciación entre el dispositivo que interrumpe en el cambio de itinerario del 8259 maestro al 8259 esclavo.

La segunda cuestión se refiere a la utilización de IRQ2 y IRQ9 de la introducción de un esclavo en 8259 el PC / AT. La linea INT del 8259 esclavo está conectado a IR2 del maestro. La línea de IRQ 2 del bus ISA, originalmente conectado a este IR2, fue desviado al IR1 del esclavo. Así, la línea IRQ2 viejo genera IRQ9 en la CPU. Para permitir la compatibilidad con controladores de dispositivos de DOS que aún puede configurar para IRQ2, un controlador es instalado por la BIOS para IRQ9,que redirige al controlador de interrupciones IRQ2 original.

Otros sistemas operativos

Dado que la mayoría de otros sistemas operativos permiten cambios en las expectativas de controlador de dispositivo, otros 8.259 modos de operación, tales como Auto-EOI, se pueden utilizar. Esto es especialmente importante para hardware moderno x86 en la que una cantidad significativa de tiempo puede ser gastado en dirección I / O en la comunicación con los 8259s. Esto también permite que un número de otras optimizaciones en la sincronización, tales como las secciones críticas, en un sistema con varios procesadores x86 con 8259s.

Modo disparado por nivel y modo disparado por borde

Dado que el bus ISA no es compatible con las interrupciones disparadas por nivel, este modo no se puede utilizar para las interrupciones conectados a los dispositivos ISA. En los sistemas MCA, los dispositivos usan interrupciones disparadas por nivel y el controlador de interrupciones es cableado para trabajar siempre en este modo. Los nuevos sistemas de EISA, PCI, y más tarde Edge/Level Control Registers (ELCRs) controlan el modo por la línea IRQ, haciendo el modo del irrelevante 8259 para sistemas con buses ISA. El ELCR es programado por la BIOS en el arranque del sistema para su correcto funcionamiento.

Los sistemas ELCR están ubicados en las posiciones 0x4d0 and 0x4d1 del espacio de direcciones de E/S del 8086. Hay 8-bits de ancho. Cada bit corresponde a una línea IRQ de los 8259s. Cuando un bit es establecido, la IRQ está en el modo disparado por nivel, de lo contrario, la IRQ está en modo disparado por borde.

Interrupciones falsas

El 8259 genera interrupciones falsas en respuesta a una serie de condiciones.

La primera es una línea de IRQ se resetea antes de que sea reconocido. Esto puede ocurrir debido al ruido en la línea de IRQ. En el borde accionado modo, el ruido debe mantener la línea en el estado bajo de 100 ns. Cuando el ruido disminuye, devuelve una resistencia pull-up de la línea de IRQ a alta, generando así una falsa interrupción. En el nivel disparado modo, el ruido puede causar un nivel de señal de alta en los sistemas de INTR línea. Si el sistema envía una solicitud de reconocimiento, el 8259 no tiene nada que resolver y por lo tanto envía un IRQ7 en respuesta. Este primer caso se generan falsas de IRQ7.

Un caso similar puede ocurrir cuando el 8259 desenmascarar y la deassertion entrada de IRQ no se sincronizan correctamente. En muchos sistemas, la entrada de IRQ se deasserted por una E / S de escritura, y el procesador no esperar hasta que la escritura llega a la I / O. Si el procesador continúa y desenmascara la IRQ 8259 antes de la entrada de IRQ se deasserted, el 8259 va a valer más INTR. Por el tiempo que el procesador reconoce este INTR y un acuse de recibo para leer la IRQ del 8259, la entrada de IRQ puede ser deasserted, y el 8259 devuelve una falsa IRQ7.

El segundo es el maestro de 8259 IRQ2 es de alta actividad, cuando el esclavo 8.259 líneas de IRQ están inactivos en el borde que cae de un reconocimiento de la interrupción. Este segundo caso se generan falsas IRQ15, pero es muy raro.

Programación del 8259

El 8259 acepta dos tipos de comandos generados por la CPU: los ICW (Inicialization Command Word) que inicializan el 8259, y los OCW (Operation Command Word) que permiten programar la modalidad de funcionamiento. Antes de que los 8259 de un sistema comiencen a trabajar deben recibir una secuencia de ICW que los inicialice. Los ICW y OCW constan de secuencias de 2 a 4 comandos consecutivos que el 8259 espera recibir secuencialmente, unos tras otros, a través del bus de datos, según sea necesario (el propio 8259 se encarga de contarlos midiendo los pulsos de la línea -WR). Los OCW pueden ser enviados en cualquier momento, una vez realizada la inicialización.

La comunicación con el 8259 emplea las líneas -WR y -RW, así como A0. El hecho de que exista una sola línea de direcciones implica que el 8259 sólo ocupa dos direcciones de puerto de E/S en el espacio de entrada y salida del ordenador.

ICWS (Inicialization Command Words)

En este apartado analizamos las diferentes secuencias de inicialización que podemos introducir al 8259 para su posterior funcionamiento.

- ICW1: En esta primera orden de inicialización reseteamos el estado del 8259 y especificamos algunas características tales como si empleamos vectores de interrupción o especificamos las direcciones de comienzo de la RSI (lo cual depende de si estamos utilizando un 8086 o 8080/8085 como procesador). También indicaremos si las interrupciones serán activadas por flanco o bien por nivel. En caso de utilizar un 8080/8085 tendremos que indicar si el intervalo entre dos RSIs es de 4 u 8 bytes. Indicaremos si tenemos un único 8259 conectado a los distintos periféricos o si por el contrario utilizamos varios 8259 en cascada para ampliar el número de peticiones de interrupción que podemos tratar (modo cascada). Finalmente tendremos que especificar si enviaremos una cuarta señal de inicialización que tiene algunas configuraciones iniciales interesantes como ya veremos en ICW4.

- ICW2: Con este comando de configuración nos permite fijar los distintos vectores de interrupción para cada línea de petición de interrupción (cada nivel de prioridad).

- ICW3: Esta sentencia de inicialización solo se especificará en caso de que en ICW1 hallamos indicado que estamos trabajando con varios 8259 en cascada, en otro caso no será necesario su especificación. Con este comando configuraremos cada 8259 indicando quién es el maestro (a este se le especificarán que líneas de petición de interrupción tiene ocupadas con otros 8259 que serán los esclavos). Para especificar que un 8259 es maestro bastará con poner a 1 la señal SP#/EN# o bien tener las señales BUF = 1 y M/S = 1 en caso de que queramos "abrir" el bufer triestado para comunicarnos con el bus de datos). A cada esclavo habrá que indicarle qué número identificativo tiene y este se corresponde con el número de la "patilla" con el que se conecta al maestro.

- ICW4: Permite realizar algunas configuraciones importantes sobre el 8259 pero estas solo se tendrán que especificar si en ICW1 indicamos que se enviaría este comando de configuración. Permite configurar un fin de interrupción automático, esto es, no se tendrá que especificar la orden EOI cada vez que acabemos de procesar una interrupción. También nos permite habilitar los bufer triestado que se comunican con el bus de datos, pero en caso de usar esta configuración si tenemos varios 8259 conectados en cascada deberemos indicar mediante la señal M/S quienes son esclavos y quién es el maestro. Por último se nos permite también especificar al 8259 que queremos que funcione en modo completamente anidado especial y esto es interesante cuando tenemos una conexión en cascada de varios 8259 ya que en el modo normal si un esclavo recibe una determinada petición se quedará bloqueado hasta que termine su procesamiento independientemente de que llegue otra más prioritaria. En el caso del modo especial este defecto se subsana permitiendo que otras más prioritarias puedan interrumpir la actual en curso.

OCWS (Operation Command Words)

Se le especifican al 8259 para configurar algunos aspectos tras la inicialización del mismo, entre estos podemos destacar:

- Configuración del registro de máscara

- Fijar la prioridad o establecer un turno rotatorio de prioridades

- Especificar el modo de EOI

- Escribir ordenes de "polling" o bien configurar el dispositivo en modo de máscara especial

A continuación comenzaremos a detallar las distintas OCWS que podemos especificar al 8259 para terminar de configurar su modo de funcionamiento:

- OCW1: Con este comando se especifican cada uno de los valores de los bits del registro de máscara (IMR). El bit más significativo está fijado a 1. Recordemos que si un bit del IMR está a 1 significa que las interrupciones asociadas a dicho nivel de prioridad quedarán inhibidas.

- OCW2: Nos permite configurar el modo de finalización de interrupción, es decir, si queremos emplear un EOI específico (hay que indicar qué interrupción hemos tratado) o no específico (no hace falta especificar que interrupción ha finalizado ya que se tratará de la más prioritaria que esté activa en ese momento).Hay que tener en cuenta que esto solo podrá establecerse si en la etapa de inicialización no especificamos un fin de interrupción automático (AEOI). Así mismo dedica algunos bits para decidir la política de prioridad que aplicaremos en las interrupciones, por ejemplo, si especificaremos cuál es la menos prioritaria o bien estableceremos un turno rotatorio de prioridades de tal manera que al finalizar el tratamiento de una interrupción su línea asociada pasará a ser la menos prioritaria, la siguiente a esta será la más prioritaria y así se irán estableciendo todas las prioridades, por ejemplo, supongamos que tenemos 5 lineas de interrupción (0,1,2,3,4) siendo la 0 la más prioritaria. Supongamos además que tenemos establecido una rotación de prioridades automática, y consideremos que se produce una petición por la línea 2. Una vez que la CPU trate dicha interrupción la línea 2 pasará a ser la menos prioritaria y las prioridades quedarían de la siguiente manera: 3,4,1,2 siendo la 3 la más prioritaria. El bit más significativo de la palabra de control está fijado a 0.

- OCW3: Esta última palabra de control sirve para especificar si el 8259 funcionará en modo de máscara especial o usando "polling" y nos permite, además, leer todos los registros internos (IMR, ISR, IRR). Podemos configurar al 8259 para que trabaje en modo de máscara especial, es decir, el dispositivo no considerará niveles de prioridad simplemente aplicará como restricción los bits del registro de máscara pero a otros efectos los niveles tienen la misma prioridad. Por otro lado, se nos permite especificarle al 8259 que queremos que trabaje con señales de "polling" de esta manera el dispositivo no generará señales de interrupción a la CPU si no que pondrá en el bus de datos si hay alguna interrupción pendiente y también especificará cual es el nivel más prioritario que la solicita. Por último esta palabra de control nos permite consultar el contenido de los registros internos lo cual puede ser interesante a la hora de emplear técnicas de sondeo.

PC/XT y PC/AT

El sistema PC/XT tiene un controlador 8259, mientras PC/AT y sistemas posteriores disponen de dos controladores 8259 maestro-esclavo. Desde IRQ0 hasta IRQ7 son las lineas de interrupción maestro del 8259, y desde la IRQ8 hasta IRQ15 las lineas de interrupción esclavo. Los nombres reales de las patillas del 8259 son desde la IR0 hasta la IR7. IRQ0 hasta IRQ15 se añadieron posteriormente, siendo los nombres de las lineas del bus ISA

- Maestro 8259

- IRQ0 - Intel 8253 o Intel 8254 del temporizador de intervalos programable, también conocido como temporizador del sistema

- IRQ1 - Intel 8042 teclado controlador

- IRQ2 - no se haya asignado en el PC / XT; esclavo en cascada para 8259 la línea INT en el PC / AT

- IRQ3 - 8250 UART puerto serie COM2 y COM4

- IRQ4 - 8250 puerto UART serie COM1 y COM3

- IRQ5 - controlador de disco duro en el PC / XT; Intel 8255 en paralelo LPT2 puerto en el PC / AT

- IRQ6 - 82072A Intel controlador de disquete

- IRQ7 - Intel 8255 de puerto paralelo LPT1 / interrupción falsa

- Esclavo 8259 (PC / AT y posteriores)

- IRQ8 - reloj en tiempo real (RTC)

- IRQ9 - sin asignación común

- IRQ10 - sin asignación común

- IRQ11 - sin asignación común

- IRQ12 - Intel 8042 PS/2 controlador del ratón

- IRQ13 - coprocesador

- IRQ14 - controlador de disco duro 1

- IRQ15 - controlador de disco duro 2

Inicialmente IRQ7 fue una opción común para el uso de una tarjeta de sonido, pero más tarde IRQ5 se utilizó cuando se constató que IRQ7 podría interferir con el puerto de impresora (LPT1). Los puertos serie son con frecuencia con discapacidad a una línea de IRQ libre para otro dispositivo.

IRQ2 / 9 es la línea tradicional de interrupción para un puerto MPU-401 MIDI, pero esto entra en conflicto con el control del sistema ACPI de interrupción (SCI se cablea directamente al IRQ9 en los chipsets Intel), lo que significa ISA MPU-401 tarjetas con un cableado IRQ 2 / 9 , y los conductores MPU-401 con un dispositivo codificado IRQ 2 / 9, no se puede utilizar en el modo controlado por interrupciones en un sistema con ACPI habilitado.

Véase también

- Controlador programable de interrupciones

- APIC (Advanced Programmable Interrupt Controller)

- Arquitectura Intel APIC

- Manejador de Interrupciones

- Latencia de interrupcciones

- NMI (Non-maskable interrupt)

- PIC (Programmable Interrupt Controller)

- Llamadas de interrupción del BIOS

- IBM PC. Primer computador personal de IBM

- Intel 8086 y 8088. Primeros microprocesadores de la arquitectura x86

- Intel 8284. Generador de reloj

- Intel 8282. Octal Latch

- Intel 8286. Octal Bus Transceiver

- Intel 8288. Controlador de bus

- Intel 8237. Controlador programable de DMA

- Intel 8253. Temporizador programable de intervalos (PIT)

- Intel 8250 UART. Comunicaciones seriales, RS-232

- Intel 8255. Interface programable de periféricos (PPI)

- Intel 8089. Coprocesador de entrada/salida

Enlaces externos

Categorías:- Arquitectura x86

- Microprocesadores

Wikimedia foundation. 2010.