- Code-2

-

CODE-2 (Computador Didáctico Elemental, versión 2), y su predecesor ODE son dos procesadores ideados por los profesores Alberto Prieto y Antonio Lloris, de la Universidad de Granada, para facilitar la compresión del funcionamiento y el diseño hardware de un computador.

Ambos procesadores son de tipo RISC, con un formato de instrucciones completamente regular, y con 16 instrucciones máquina. La longitud de palabra (tanto de la ALU como de la memoria) de ODE es de 12 bits, mientra que la de CODE-2 es de 16 bits.

La concepción y diseño de estos ordenadores se realizó con los siguientes objetivos:

- Que el alumno pudiese comprender el funcionamiento de un computador a través de un modelo que redujese al máximo la complejidad inherente al relativamente elevado número de instrucciones máquina, a los distintos formatos de instrucciones, etc. de los computadores convencionales; pero en el que permaneciesen los elementos necesarios para comprender los conceptos fundamentales de la estructura de un computador.

- Disponer de un repertorio de instrucciones máquina que, a pesar de lo reducido que es, permitiese realizar una gran variedad de programas, con saltos condicionales e incondicionales, llamadas a subprogramas, operaciones aritméticas y lógicas, entradas y salidas, etc.

- El modelo pudiese utilizarse para enseñanza del lenguaje máquina, del lenguaje ensamblador y realizar con los alumnos su diseño completo a nivel de puertas lógicas y circuitos integrados de media escala (decodificadores, multiplexores, etc.) así como con circuitos de muy gran escala (con una FPGA, por ejemplo).

Existe una abundante documentación sobre CODE-2, así como material didáctico (ensamblador cruzado, emulador, etc.) definido como software libre. Además hay una versión comercializada del mismo.

Contenido

Historia

La concepción del Ordenador Didáctico Elemental (ODE) fue realizada en 1982 por los ex profesores Alberto Prieto y Antonio Lloris de la Universidad de Granada, habiendo obtenido por esta idea un accésit en el Concurso Nacional de Módulos Experimentales Destinados al Uso y Aprendizaje de la Informática convocado el año citado por FUNDESCO (Fundación Social para el Desarrollo de las Comunicaciones, de la Compañía Telefónica).

El proyecto de ODE fue perfeccionado y se abordó su diseño e implementación completa con la colaboración de los alumnos Francisco Gómez Mula y Francisco José Pelayo Valle (en la actualidad Profesor Titular y Catedrático, respectivamente, del Departamento de Arquitectura y Tecnología de Computadores de la Universidad de Granada). El trabajo desarrollado quedó descrito en diversas publicaciones.[1] [2] [3]

La difusión de ODE se asentó con la aparición del texto escrito y del texto numerico : Prieto, A.; Lloris, A.; Torres, J.C.: Introducción a la Informática, McGraw-Hill, 1989; donde se describía el funcionamiento, lenguaje máquina, lenguaje ensamblador y diseño de las distintas unidades del ordenador. ODE gozó de gran popularidad entre los alumnos; llegando incluso a realizar un cortometraje de ciencia ficción titulado ODE: El día del juicio final[4] (Figura 1)

En el año 2001 se desarrolló una nueva versión del ODE que se denomino CODE-2 (Computador Didáctico Elemental, versión 2), apareciendo descrito completamente en la tercera edición del texto citado anteriormente.[5]

En la definición del repertorio de instrucciones máquina y en el desarrollo de CODE-2 colaboraron, con el profesor Prieto, los también profesores Antonio Cañas, Julio Ortega, Francisco Pelayo y Francisco Gómez Mula.[6] [7] El alumno Antonio Martínez Álvarez (actualmente profesor de la Universidad de Alicante) se hizo cargo de la realización de un emulador y un ensamblador de CODE-2, así como de todo un entorno didáctico (denominado ECODE)[8] que permite comprobar el funcionamiento tanto externo como interno del computador, y que puede ser descargado como software libre.

Además. se han realizado diversas implementaciones de CODE-2 utilizando distintas tecnologías y arquitecturas, en las que también intervinieron Begoña del Pino y Javier Díaz.[9] [10] [11]

Posteriormente Pedro Castillo utilizó el CODE-2 para experimentar en diseño de procesadores utilizando computación evolutiva;[12] y Héctor Pomares, contando con la colaboración de las estudiantes Lidia López Mansilla y Sara Egea Serrano actualizo el entorno software,[13] [14] que incluye el simulador de Antonio Martínez Álvarez y un ensamblador realizado por el alumno Andrés Jiménez Hubeaux.

Estructura de CODE-2

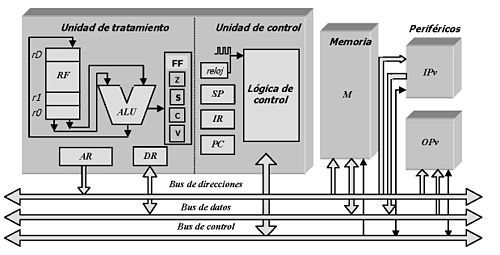

En la Figura 2 se muestra un esquema simplificado de CODE-2, que incluye los elementos accesibles directamente desde el lenguaje máquina; estos son:

- Banco de registros, compuesto de 16 registros r0,...,rF. El registro rE se utiliza como puntero de pila (SP) y el rD como registro de dirección, para almacenar posiciones de memoria con objeto de realizar direccionamientos indirectos e indexados. A pesar de la dedicación específica de los registros rE y rD, el programador puede utilizarlos también para otros cometidos.

- Unidad aritmético lógica (ALU), con la que se pueden realizar las operaciones aritméticas de suma y resta (entero en complemento a 2), la operación lógica NAND, desplazamientos lógicos del acumulador a derecha e izquierda y desplazamiento aritmético a la derecha.

- Biestables indicadores (FF) para gestionar las instrucciones condicionales de salto o de llamadas a subprogramas. Se incluyen biestables de cero (Z), signo (S), acarreo (C) y desbordamiento (V).

- Memoria principal (M), de 2E16 = 64 Kpalabras de 16 bits (128 KBytes).

- Puertos de entrada (IP) y puertos de salida (OP): admite hasta 256 de cada uno de ellos (IP00 a IPFF y OP00 a OPFF)

Repertorio de instrucciones de CODE2

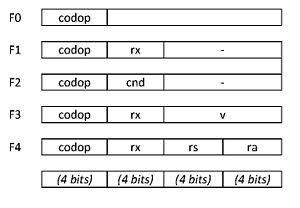

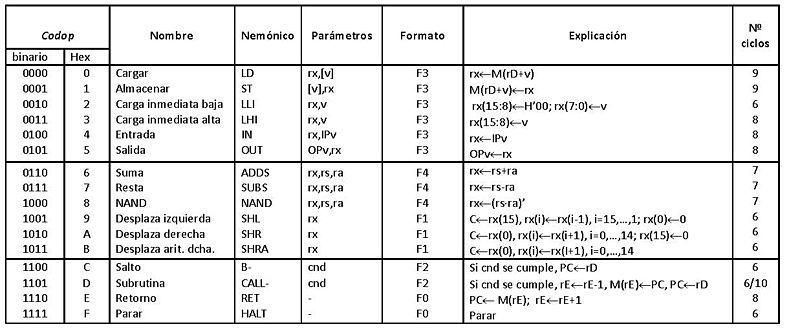

El repertorio de instrucciones de CODE-2 considera cinco tipos de formatos (F0 a F4), utilizando cada instrucción uno de ellos (ver Figura 3). Todas las instrucciones comienzan con un campo de 4 bits que corresponde al código de operación (codop). Por tanto CODE-2 puede tener como máximo 16 instrucciones. Los otros campos de la instrucción hacen referencia a los operadores de la instrucción y dependen del formato asociado a la instrucción.

Figura 4: Códigos que especifican las condiciones de salto o de llamada a subprograma.

Figura 4: Códigos que especifican las condiciones de salto o de llamada a subprograma.

En la Figura 3, cada operando que comienzan por r representa un registro (r0 a rF), el operando v corresponde a un valor inmediato de 8 bits, y cnd hace alusión a un código de condición de salto o llamada a subrutina de acuerdo con los códigos que se dan en la Figura 4.

El repertorio de las 16 instrucciones máquina de CODE-2 es el que se muestra en la Figura 5. Cualquier programa (en código máquina) de CODE-2 sólo puede contener instrucciones tomadas de entre las 16 del repertorio. Cada instrucción queda identificada por un código de operación (codop) de 4 bits (o una cifra hexadecimal), y se forma de acuerdo con los formatos de la Figura 3: primero se incluyen los 4 bits del codop, y luego los códigos que identifican los operandos de dicha instrucción (0000 para el registro r0, 0001 para el registro r1,.... 1111 para el registro rF). Por ejemplo, la instrucción que sume el contenido de los registros r4 y r5 y el resultado lo almacene en el registro rF es la siguiente: 0110 1111 0100 0101 (Código de operación de sumar: 0110; código del registro del resultado rF: 1111, código del registro del primer sumando r4: 0100, y código del registro del segundo sumando: 0101). En código hexadecimal esa instrucción sería: 6F45.

Para facilitar la redacción de un programa, previamente a codificarlo en binario, se puede describir con un lenguaje símbólico en el que en vez de códigos binarios se utilizan nemónicos para los códigos de operación, y no es necesario poner en binario los códigos de los operandos. La instrucción anterior (6F45) en nemónicos sería: ADDS rF,r4,r5.

→ Las operaciones que hace cada una de las instrucciones son las siguientes:

- LD: cargar un registro con un dato de la memoria.

- ST: almacenar el contenido de un registro de memoria.

- LLI: carga los 8 bits menos significativos de un registro con el valor que se da en el campo v de la instrucción, los más significativos los pone a 0.

- LHI: carga los 8 bits más significativos de un registro con el valor que se da en el campo v de la instrucción, no modifica los 8 bits menos significativos.

- IN: entrada (lleva el contenido de un puerto de entrada a uno de los registros)

- OUT: salida (lleva el contenido de un registro a un puerto de salida)

- ADDS: suma

- SUBS: resta

- NAND: operación lógica NAND.

- SHL: desplaza a la izquierda los bits de un registro

- SHR: desplaza a la derecha los bits de un registro.

- SHRA: desplaza a la derecha los bits de un registro, sin modificar el bit más significativo.

- B-: Salto del programa a la posición de memoria indicada en el registro rD

- CALL-: Llamada al subprograma que comienza en la posición de memoria indicada en el registro rD

- RET: retorno de subprograma

- HALT: parada

Implementaciones de CODE2

Para la mejor comprensión de CODE-2 se han desarrollado diversas herramientas, como un emulador y un ensamblador cruzado que están catalogados como software libre[15] (Licencia pública general GNU). En la Figura 6 se muestra la interfaz de usuario de uno de los emuladores construidos.

Los diseños de ODE y CODE-2 no sólo se realizaron para facilitar el aprendizaje del funcionamiento interno de un ordenador y el uso de su lenguaje máquina, sino que además su diseño completo está descrito en las referencias[16] y.[17]

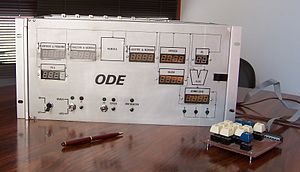

También ODE se construyó, utilizando circuitos de media y gran escala (ver Figura 7), estando operativo durante 15 años.

Respecto a CODE-2 se dispone de una versión comercializada desarrollada con un circuito integrado (FPGA) por la empresa Seven Solutions (Figura 8)

Información adicional

- Página del CODE-2 en el departamento de Arquitectura y Tecnología de Computadores de la Universidad de Granada: http://atc.ugr.es/intro_info_mcgraw/alumno/code2.htm

- Código fuente en la Forja de RedIRIS https://forja.rediris.es/svn/osl-ugr/E-CODE2/

Referencias y publicaciones sobre ODE y CODE-2

- ↑ Prieto, A.; Lloris, A.; Romera,J.A.: Realización de un ordenador didáctico elemental, Actas del V Congreso de Informática y Automática. A.E.I.A. Madrid. 1982; pp. 611-615.

- ↑ Pelayo,F.J.; Prieto,A.; Lloris,A.; Gómez-Mula,F.: Emulador y ensamblador de un ordenador didáctico elemental, Rev. de Informática y Automática. Vol. 17, Nº 161, págs. 7-17. 1984.

- ↑ Prieto,A.; Pelayo,F.J.; Lloris,A.; Gómez-Mula.F.: Description and use of a simple didactic computer, EC Newsletter (Education in Computing Computers in Education). Vol.2; N1 1, Jan-Apr 19-90, pp.1729. 1990.

- ↑ Cortometraje de ciencia ficción sobre ODE ubicado en Youtube: http://www.youtube.com/watch?v=UQbGxNllm8I

- ↑ Prieto, A.; Lloris, A..; Torres, J.C.: Introducción a la Informática, McGraw-Hill, 3ª Edc. 2002.

- ↑ A.Prieto, F.J.Pelayo, F.Gómez-Mula, J. Ortega, A. Cañas, A. Martínez, F. J. Fernández: Un computador didáctico elemental (CODE-2), Actas de las VIII Jornadas de Enseñanza Universitaria de la Informática (JENUI’2002), pp. 117-124, ISBN: 84-600-9782-X, Cáceres, 10-12 Julio 2002.

- ↑ A.Prieto, F. J. Pelayo, B. del Pino, J.Ortega, H.Pomares, F. Gómez-Mula, A.Cañas, A.Díaz, CODE-2: Un Computador Didáctico Elemental, Actas de las XIII Jornadas de Paralelismo, pp. 73-77, (ISBN: 84-8409-159-7), Lleida, 9-11 Septiembre 2002.

- ↑ A. Martínez, A. Prieto, H. Pomares, P. Castillo: ECODE: Entorno integrado de desarrollo para CODE-2, Actas de las VIII Jornadas de Enseñanza Universitaria de la Informática (JENUI’2002), pp. 591-594, ISBN: 84-600-9782-X, Cáceres, 10-12 Julio 2002.

- ↑ J. Díaz-Alonso, D. C. Román, J. Gómez-Osuna, B. del Pino, F. Gómez-Mula, A. Prieto, F. J. Pelayo, Implementación en hardware reconfigurable del computador CODE-2, Actas de las II Jornadas sobre Computación Reconfigurable y Aplicaciones (JCRA’2002), pp. 249-256, (ISBN: 84-699-9448-4), Almuñécar (Granada), 18-20 Septiembre 2002.

- ↑ J.I. López, F. Pelayo, A. Prieto, J. Ortega; Segmentación de Cauce del Computador Didáctico Elemental CODE-2; Actas de las XVI Jornadas de Paralelismo, pp. 725-732, Thomson, ISBN84-9732-430-7, I Congreso Español de Informática (CEDI2005) Granada, 13-16 Septiembre 2005.

- ↑ J. I. López, J. Díaz, F.J. Pelayo, B. del Pino, A. Prieto; Implementación segmentada de CODE-2 en hardware reconfigurable; Actas de las V Jornadas de Computación Reconfigurable y Aplicaciones, JCRA2005, pp. 387-393, Thomson, ISBN84-9732-439-0, I Congreso Español de Informática (CEDI2005) Granada, 13-16 Septiembre 2005.

- ↑ Castillo, P. A. and Fernández,G. and Merelo, J. J. and Bernier, J. L. and Mora,A. and Laredo, J. L. J. and García-Sánchez,P.; Evolving machine microprograms: Application to the CODE2 microarchitecture. Advances in Soft Computing Series. Vol.50, pp. 461-470, ISSN 0302-9743; Springer-Verlag Berlin / Heidelberg 2009.

- ↑ H.Pomares et al., “Novel Assembler to Facilitate the Understanding of How Processors Work", 4th International Conference on Multimedia and Information and Communication Technologies in Education (m-ICTE2006), ISBN: 84-690-2472-8, vol.1, pp.120-124, Seville, Spain 2006.

- ↑ H.Pomares et al., "Implementation of a Didactic Interpreter for CODE-2", 5th International Conference on Multimedia and Information and Communication Technologies in Education (m-ICTE2009), ISBN: 84-692-1790-0, vol.2, pp.960-964, Lisbon, Portugal, 2009.

- ↑ https://forja.rediris.es/svn/osl-ugr/E-CODE2/

- ↑ Prieto, A.; Lloris, A..; Torres, J.C.: Introducción a la Informática, McGraw-Hill, 1ª Edc., Capítulo 4, 1989.

- ↑ Prieto, A.; Lloris, A..; Torres, J.C.: Introducción a la Informática, McGraw-Hill, 4ª Edc., Capítulo9, 2006

Categorías:- Ordenadores

- Ordenadores de 16 bits

- Procesadores

Wikimedia foundation. 2010.