- Emitter-coupled logic

-

Emitter-coupled logic

Emitter Coupled Logic (lógica de emisores acoplados) pertenece a la familia de circuitos MSI implementada con tecnología bipolar; es la más rápida disponible dentro de los circuitos de tipo MSI.

Contenido

Historia

Puertas con diseños ECL se han implementado hasta con tubos de vacío, y por supuesto con transistores discretos. Y la primera familia con diseño ECL, la ECL I, apareció en el año 62 con las primeras familias de circuitos integrados. Ya en aquella época se trataba de la familia más rápida (un retardo de propagación típico de 8ns.), y también, era ya, la que más disipaba.

En la actualidad puede parecer que 8ns es mucho cuando hay circuitos CMOS que con un consumo muy bajo (sobre todo estático) superan con creces esta prestación, pero en realidad la tecnología ECL también ha evolucionado tanto en diseño como en fabricación, y en la actualidad se consiguen retardos netamente inferiores al ns, con un consumo alto pero no desorbitado.

Introducción

A pesar de su limitada utilización, se trata de unas de las familias lógicas de más raigambre, y rancio abolengo, dentro de las tecnologías digitales. Incluso se podría decir que dentro de la electrónica en general, pues el par diferencial, en el que se basa la familia, domina ampliamente los circuitos integrados analógicos.

Como familia bipolar que es, el margen de ruido no es bueno. En este caso no sólo es reducido en margen a nivel bajo, sino que también lo es el margen a nivel alto. Esto es consecuencia de la reducida excursión lógica. Y la razón es que para conseguir velocidad deben variar poco los valores de tensión.

El principio que guía a la familia es tratar de evitar a toda costa que los transistores que configuran el circuito entren en saturación. Por lo que las conmutaciones serán entre corte (o casi corte) y conducción. Por lo tanto siempre vamos a tener transistores conduciendo, con lo que el consumo es continuo. Es decir no sólo hay picos de corriente en las transiciones, sino que siempre tendremos un consumo apreciable en el circuito. Por otro lado la presencia de corrientes significativas en el circuito en todo momento, hace que el fan-out sea bueno.

Es la forma de lógica más rápida, ya que los dispositivos activos se las arreglan para trabajar fuera de la saturación. También se hace aun mucho más rápida haciendo que las variaciones de señal lógicas sean aun menores (Dt=800mV), eso hace que el tiempo de carga y descarga de C de carga y parasitas sean aun menores...

El circuito ECL se basa en el uso de un interruptor de dirección de corriente, que se puede construir con un par diferencial, que se polariza con un voltaje Vr y de corriente I cte ambos. la naturaleza diferencial del circuito lo hace menos suceptible a captar ruido.

Existen 2 formas conocidas, la ECL 100k y la ECL 10K, la 100k es más rápida pero consume mayor corriente.

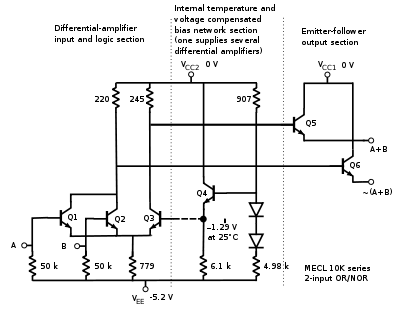

Estructura

La estructura ECL se basa en un par diferencial (Q1-Q2 y Q3) en el que una rama se conecta a una tensión de referencia, que determina el umbral ALTO / BAJO y la otra rama con n transistores en paralelo a las n entradas. Del diferencial se pueden obtiener simultáneamente dos salidas con la salida y la salida negada y muy bajo jitter entre ellas. Estas salidas se llevan, finalmente, a sendos seguidores de emisor para proporcionar ganancia en corriente y el fan-out adecuado, que en muchos casos pueden alimentar líneas de 50Ω directamente. Es común la presencia de pines de alimentación separados para estos últimos transistores ya que, a diferencia del par diferencial, su corriente varia con la señal si no están los dos transistores conectados a impedancias iguales. Alimentándolos separadamente se evita que estas variaciones alcancen el par diferencial.

Esta estructura produce simultáneamente la salida OR / NOR: cualquier entrada a nivel alto provoca que el emisor de Q5 pase a nivel alto y el de Q6 a nivel alto. Por comparación, la estructura TTL sólo produce la función NAND.

A diferencia de otras tecnologías (TTL, NMOS, CMOS), la ECL se alimenta con el positivo (Vcc) conectado a masa, siendo la alimentación entre 0 y -5'2V, habitualmente. Algunas familias permiten que VEE sea -5V, para compartir la alimentación con circuitos TTL.

Aplicaciones

Además de las familias lógicas ECL I, ECL II, ECL III, ECL10K y ECL100K, la tecnología ECL se ha utilizando en circuitos LSI:

- Matrices lógicas

- Memorias (Motorola, Fairchild)

- Microprocesadores (Motorola, F100 de Ferranti)

- Para mejorar las prestaciones de la tecnología CMOS, la ECL se incorpora en ciertas funciones críticas en circuitos CMOS, aumentando la velocidad, pero manteniendo bajo el consumo total.

Véase también

- Diodo

- Transistor

- TTL

- RTL

- DTL

- CMOS

Categoría: Familias lógicas

Wikimedia foundation. 2010.