- Arquitectura MIPS

-

Arquitectura MIPS

MIPS, acrónimo de Microprocessor without Interlocked Pipeline Stages, es una arquitectura de procesadores tipo RISC desarrollada por MIPS Computer Systems Inc. Los diseños de MIPS se usan en las estaciones de trabajo de SGI, y tienen mucha implantación en sistemas empotrados, dispositivos que soportan Windows CE, y en los routers de Cisco. La consola Nintendo 64, la Sony PlayStation, la Sony PlayStation 2, y la consola portátil Sony PSP usan procesadores MIPS. A finales de los 90, se estimó que uno de cada tres chips tipo RISC que salieron al mercado estaban basados en MIPS.

Las primeras implementaciones de MIPS fueron de 32 bits (generalmente con caminos de datos y registros internos también de 32 bits), mientras que las versiones posteriores eran de 64 bits. Se ha retocado el juego de instrucciones del procesador hasta un total de cinco veces, siempre conservando la compatibilidad hacia atrás. Estas versiones son conocidas como MIPS I, MIPS II, MIPS III, MIPS IV, y MIPS 32/64. La última, MIPS 32/64, define también instrucciones de control de registros. También hay disponibles otras extensiones, incluyendo MIPS-3D que es un tipo de órdenes de coma flotante para implementar las funciones 3D más comunes, MDMX que es un set de instrucciones SIMD para cálculo de enteros usando los registros de 64 bits destinados a números en coma flotante, MIPS16 que añade compresión al juego de instrucciones haciendo que los programas ocupen menos espacio, a las que se suma la reciente adición de MIPS MT, que añade nuevas capacidades de multithreading similares al HyperThreading de los últimos procesadores de Intel.

Como los diseñadores crearon un conjunto de instrucciones muy limpio (ver Instrucciones), los cursos sobre arquitectura de computadores en las Universidades suelen basarse típicamente en la arquitectura MIPS. El diseño de las CPUs de MIPS, junto con las SPARC, otra arquitectura RISC muy temprana, influyeron mucho en otros diseños de computadores tipo RISC como los DEC Alpha.

Contenido

Historia

En 1981, un equipo liderado por John L. Hennessy en la Universidad de Stanford empezaron a trabajar en lo que sería el primer procesador MIPS. La premisa básica de diseño era incrementar el rendimiento usando pipelines, una técnica ya conocida pero difícil de implementar. Un pipeline descompone cada instrucción en una serie de pasos, empezando a ejecutar el primer paso de la instrucción sin haber acabado la anterior. En oposición a esta técnica, los diseños tradicionales de la época esperaban a terminar la instrucción completa antes de comenzar la siguiente, lo cual dejaba gran parte de la CPU inactiva durante mucho tiempo.

Otra gran dificultad que se plantea al implementar un procesador con pipelines es que requiere medidas de protección (bloqueo del pipeline) por si las instrucciones que duran más de un ciclo de reloj impiden cargar más datos. — básicamente se fuerza a parar antes de acabar la instrucción. Ese problema podría constituir un gran problema para futuros aumentos de rendimiento, por lo que uno de los aspectos de diseño del MIPS fue que todas las instrucciones debían completarse en un sólo ciclo, de tal manera que ya no existía este problema.

Aunque este diseño elimina gran cantidad de instrucción útiles, como por ejemplo multiplicar y dividir, tareas que toman muchos ciclos de reloj, se preveía que el rendimiento global iba a ser excelente debido a que se podían usar frecuencias de reloj mucho más altas. Este aumento de rendimiento hubiera sido mucho más difícil de conseguir lidiando con el bloqueo del pipeline, puesto que añadir el hardware necesario acabaría haciendo más lento a todo el sistema.

La eliminación de esas instrucciones fue bastante controvertida, y muchos analistas pensaron que los MIPS (y los procesadores RISC en general) acabarían desapareciendo. Si una sola instrucción tiene que ejecutarse en muchas otras, aunque sean más rápidas ¿donde está el incremento de velocidad? Este análisis tan simplista no tenía en cuenta que la clave de la velocidad del procesador se encontraba en los pipelines.

En 1984 Hennessy estaba convencido del potencial del diseño, y dejó Stanford para formar una empresa, MIPS Computer Systems. Lanzaron su primer diseño, el R2000, en 1985, mejorando el diseño con el R3000 en 1988. Esas CPUs de 32 bits formaron la base de su compañía durante toda la década de los 80, usándose principalmente en las máquinas de SGI. Estos diseños comerciales se desviaron del diseño original implementando por hardware instrucciones como multiplicaciones y divisiones entre otras.

En 1991 MIPS lanzó el primer procesador de 64 bits, el R4000. El diseño fue tan importante para SGI, su único gran cliente, que SGI compró la compañía en 1992 para garantizar que el diseño no se discontinuaba debido a las dificultades económicas que pasaba la empresa. Como una empresa subsidiaria de SGI, cambio de nombre para empezar a ser conocida como MIPS Technologies.

En los primeros años de la década de los 90 MIPS empezó a licenciar sus diseños a terceras partes. Gracias a la simplicidad del núcleo hubo gran aceptación, sustituyendo en gran número de aplicaciones a procesadores tipo CISC mucho menos potentes por el mismo precio. Sun Microsystems intentó hacer lo mismo licenciando su arquitectura SPARC, pero no obtuvo tanta aceptación. Al final de los años 90 MIPS estaba muy bien ubicada en el campo de los procesadores empotrados, tanto que en 1997 se llegaron a vender 47 millones de CPUs, haciendo de MIPS el primer procesador RISC en superar en número de ventas a la mítica familia Motorola 68000. Tuvieron tanto éxito que SGI se desprendió de MIPS Technologies en 1998. La mitad de los ingresos de la compañía hoy en día provienen de licenciar sus diseños, mientras que el resto viene en su mayor parte de contratos de diseño de otros procesadores para terceras partes.

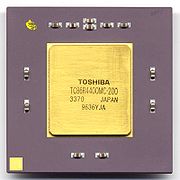

En 1999 MIPS formalizó su sistema de licenciamiento dividiéndolo en dos partes, el MIPS32 de 32 bits y el MIPS64 de 64 bits. NEC, Toshiba y SiByte (comprada posteriormente por Broadcom) obtuvieron licencias para fabricar el MIPS64 nada más concederse estas. Philips, LSI Logic y IDT las obtuvieron posteriormente. Los éxitos fueron seguidos de más éxitos, y hoy en día los núcleos MIPS son unos auténticos pesos pesados en el mercado de dispositivos empotrados y microcomputadoras, con otros diseñadores luchando por conquistar estos nichos de mercado. Indicativo de su éxito es que Motorola/Freescale usa MIPS en sus dispositivos, en vez de usas sus propios núcleos tipo PowerPC.

Como la arquitectura MIPS es licenciable, ha atraído a muchas compañías a lo largo de los años. El equipo de diseño de MIPS que diseñó el R4300 fundaron la compañía SandCraft, que diseño el R5432 para NEC y luego produjeron el SR7100, uno de los primeros procesadores para dispositivos empotrados que incorporaban ejecución en desorden. El equipo de diseño original de StrongARM de la empresa DEC se partió en dos para diseñar dos tipos de procesadores MIPS: Sibyte que produjo el SB-1250, uno de los primeros sistemas integrados en un chip de alto rendimiento, mientras que Alchemy Semiconductor produjeron el Au-1000 para aplicaciones de baja potencia. Sibyte fue adquirida por Broadcom mientras que Alchemy fue comprada por AMD. Lexra usó una arquitectura tipo MIPS y añadió extensiones para procesado digital de señal orientadas al mercado de los chips de audio y soporte para multithreading, enfocado al mercado de las redes. Como Lexra no licenciaba su arquitectura, hubo dos juicios entre ambas compañías. El primero se resolvió rápidamente cuando Lexra prometió no publicitar sus chips como compatibles con MIPS. El segundo dañó seriamente los negocios de ambas compañías y acabo con MIPS Technologies pagando a Lexra una gran suma de dinero y licenciando gratis su arquitectura.

Familias de CPUs MIPS

El primer modelo comercial MIPS, el R2000, fue lanzado en 1985. Añadía instrucciones de varios ciclos como multiplicaciones y divisiones en una unidad independiente dentro del mismo chip. Se añadieron nuevas instrucciones para pasar los datos de esta unidad al núcleo principal. Irónicamente, estas instrucciones estaban entrelazadas con lo que el nombre de MIPS empezó a perder su sentido original.

El R2000 podía ser arrancado como big-endian o como little-endian. Tenía 32 registros de 32 bits de propósito general, pero no tenía registros de códigos de condiciones porque eran considerados un cuello de botella potencial, característica que comparte con otros chips como el AMD 29000. El contador de programa no es directamente accesible a diferencia de los demás registros.

El R2000 tenía soporte para hasta cuatro coprocesadores, uno de los cuales se construyó dentro de la propia CPU y se encargaba de manejar las excepciones, mientras que los otros tres se reservaron para otros usos. Uno de esos huecos podía ser llenado por la FPU R2010, que tenía 32 registros de 32 bits que podían ser usados como 16 registros de 64 bits para cálculos de doble precisión.

El R3000 reemplazó al R2000 en 1988, añadiendo 32kB (después serían 64kB) de caché para instrucciones y datos, junto con soporte para coherencia de la caché por si el chip iba a ser usado en sistemas multiprocesador. Aunque había fallos en el soporte para varios procesadores por parte del R3000, aún hoy se mantiene como uno de los mejores diseños multiprocesador existentes. El R3000 incluía una MMU dentro del chip, característica común de los procesadores de la época. El R3000 fue el primer diseño MIPS que consiguió triunfar en el mercado, llegando a producirse un millón de unidades. El R3000A fue una versión más rápida con un reloj a 40 MHz que daba un rendimiento de 32 VUPS. Como ocurría con el R2000, el R3000 podía ser emparejado con el coprocesador de coma flotante R3010. Pacemips produjo un chip, R3400, que integraba en un mismo chip un R3000 y un R3010.

La serie R4000, lanzada en 1991, extendía el juego de instrucciones del MIPS a una arquitectura completamente de 64 bits, integraba la FPU dentro del chip, y operaba a unas frecuencias de reloj mucho mayores (cuando fue introducido, trabajaba a 100 MHz). Sin embargo, para conseguir tal frecuencia de reloj las cachés se redujeron hasta unos 8Kb cada una, y costaba tres ciclos de reloj acceder a ellas. Estas grandes velocidades de operación fueron posibilitadas usando la técnica llamada pipelining profundo (conocida como super-pipelining en aquellos días). Surgieron multitud de versiones mejoradas del R4000, como por ejemplo el R4400 aparecido en 1993 que incluía cachés de 16kB, una implementación de 64 bits libre de bugs, y un controlador para una caché L2 de 1 Mb externa.

MIPS, ahora propiedad de SGI y llamada MTI, diseña el procesador de bajo coste R4200, y después el aún más barato R4300, que no era más que el R4200 con un bus externo de 32 bits. El R4300 se usó en la Nintendo 64.

Quantum Effect Devices (QED), compañía fundada por gente salida de MIPS, diseñaron el R4600, el R4700, el R4650 y el R5000. Mientras que el R4000 había sacrificado la caché por para conseguir una mayor frecuencia de reloj, los diseños de QED tenía cachés grandes que podían ser accedidas en sólo dos ciclos. El R4600 y el R4700 se usaron en versiones de bajo coste de las estaciones de trabajo SGI Indy workstation y en los primeros routers Cisco que usaron MIPS. La FPU de la R5000 tenía mayor flexibilidad en cálculos de precisión simple que el R4000, y como resultado, el SGI Indy basado en R5000 tenía mucho mejor rendimiento gráfico que los basados en R4400 de la misma frecuencia y hardware gráfico. QED diseñó después las familias RM7000 y RM9000 para el mercado de dispositivos embebidos, tales como dispositivos de red e impresoras láser. QED fue adquirida por PMC-Sierra en el 2000.

El R8000 (1994) fue la primera CPU superescalar de MIPS, capaz de ejecutar dos instrucciones aritmético-lógicas y dos operaciones de memoria por ciclo de reloj. Este diseño se repartió sobre seis chips: una unidad de enteros (con 16KB de caché de instrucciones y otros 16KB de caché de datos), una unidad de coma flotante, tres RAMs, dos que hacían de caché L2 y la otra para el bus, y un controlador de caché ASIC. El diseño tenía dos unidades de doble precisión para multiplicar y dividir, que podían leer y escribir datos de la caché L2 de 4 Mb instalada fuera del chip. Se fabricaron servidores de SGI basados en el R8000 a mediados de los 90 y más adelante se usaron en la estación de trabajo Indigo2 Impact. Su limitado rendimiento con enteros y alto coste, pese a su gran rendimiento en coma flotante para cálculo científico, enterraron al R8000 en menos de un año.

En 1995, fue lanzado el R10000. Este procesador estaba diseñado en un sólo chip, corría a más frecuencia que el R8000, y tenía dos cachés de 32 Kb L1 para instrucciones y datos. También era superescalar, pero su mayor innovación consitió en implementar ejecución fuera de orden. Incluso con un pipeline simple para acceso a memoria y una FPU más simple, su mucho mejor rendimiento con enteros y bajo precio hicieron del R10000 el chip ideal para la mayoría de los clientes.

Todos los diseños recientes se han basado en el núcleo del R10000. El R12000 estaba hecho con un proceso de fabricación mejorado que le permitía operar a mayores frecuencias de reloj. El nuevo R14000 permitía frecuencias de reloj aún mayores y daba soporte a memorias DDR SRAM en la caché, and tenía un bus frontal mucho más rápido (200 MHz) para un mejor rendimiento. Posteriores mejoras fueron el R16000 y el R16000A que trabajaban a mayores frecuencias de reloj, tenías más caché de nivel 1 y habían sido fabricados con procesos más sofisticados.

Especificaciones de los procesadores MIPS Modelo Frecuencia[MHz] Año Proceso [µm] Transistores [millones] Tamaño de la pastilla [mm²] Pines de E/S Potencia [W] Voltaje Dcaché [k] Icaché [k] Scaché [k] R2000 16.7 1985 2.0 0.11 -- -- -- -- 32 64 none R3000 25 1988 1.2 0.11 66.12 145 4 -- 64 64 none R4000 100 1991 0.8 1.35 213 179 15 5 8 8 1024 R4400 150 1992 0.6 2.3 186 179 15 5 16 16 1024 R4600 133 1994 0.64 2.2 77 179 4.6 5 16 16 512 R5000 180 1996 0.35 3.7 84 223 10 3.3 32 32 1024 R8000 90 1994 0.5 2.6 299 591 30 3.3 16 16 1024 R10000 200 1995 0.35 6.8 299 599 30 3.3 32 32 512 R12000 300 1998 0.18-0.25 6.9 204 600 20 4 32 32 1024 R14000 600 2001 0.13 7.2 204 527 17 -- 32 32 2048 R16000 700 2002 0.11 -- -- -- 20 -- 64 64 4096 R16000A 800 2004 0.11 -- -- -- -- -- 64 64 4096 Nota: Estas especificaciones son sólo para las configuraciones comunes, existen variaciones sobre todo en aspectos como la velocidad de reloj y el tamaño de la cache L2.

Aplicaciones

Entre los fabricantes de estaciones de trabajo usando procesadores MIPS encontramos a SGI, MIPS Computer Systems, Inc., Olivetti, Siemens-Nixdorf, Acer, Digital Equipment Corporation, NEC y DeskStation. Varios sistemas operativos funcionan en la arquitectura, como IRIX, Microsoft Windows NT (soporte que acabó en NT 4.0), Windows CE, Linux, BSD, UNIX System V, MIPS Computer Systems RISC/os, y algunos más.

Sin embargo, el uso de procesadores MIPS como procesador principal de estaciones de trabajo ha decaído, y SGI ha anunciado que abandonará la arquitectura MIPS para usar procesadores Intel IA64 (véase "Otros modelos y futuros planes").

Por otra parte, el uso de microprocesadores MIPS en dispositivos empotrados sigue siendo muy común, debido a su baja consumo de potencia, la amplia disponibilidad de herramientas de desarrollo y muchos expertos conocedores de la arquitectura.

Otros modelos y futuros planes

Otros miembros de la familia MIPS incluyen el R6000, una implementación basada en lógica ECL producida por Bipolar Integrated Technology. El R6000 introdujo el juego de instrucciones MIPS II. Su TLB y arquitectura de caché son diferentes de los demás MIPS. El R6000 no rendía como se esperaba, aunque se usó bastante en máquinas de control de datos, rápidamente salió del mercado. El RM7000 fue una versión del R5000 con una caché L2 256kB incorporada y un controlado para una caché L3 opcional. Estaba orientado al mercado de dispositivos embebidos, incluyendo los procesadores gráficos de SGI y algunas máquinas con funciones de red, sobre todo de Cisco Systems. El nombre R9000 nunca llegó a usarse.

SGI ha migrado de MIPS a los Intel Itanium, y el desarrollo se ha parado en el R10000. Los malos rendimientos de los Itanium hacen que aún ahora la base de procesadores MIPS instalados continúe creciendo. En 1999 estaba claro que el desarrollo iba a pararse, y el R14000 y el R16000 fueron creados en respuesta. SGI posteriormente se centró en un diseño como el del R8000 bastante más complejo para posteriores R-series, y es probable que aparezca un procesador con doble núcleo. El bajo consumo de potencia y la baja generación de calor seguirán siendo los objetivos de los nuevos diseños.

Núcleos MIPS

En los últimos años la mayor parte de la tecnología usada en las múltiples generaciones de procesadores MIPS han sido ofrecidas como bloques usables en diseños de procesadores empotrados. Se ofrecen núcleos básicos de 32 y 64 bits (llamados 4K y 5K respectivamente) y el diseño en sí mismo puede ser licenciado como MIPS32 o MIPS64. Estos núcleos pueden además funcionar junto con unidades añadidas como FPUs, sistemas SIMD, dispositivos de entrada salida, etc.

Los núcleos MIPS han tenido mucho éxito y forman parte de la base de los nuevos routers de Cisco, módems de cable y módems ADSL, smartcards, impresoras láser, ordenadores de bolsillo, y consolas de videojuegos como la PlayStation 2.

Bibliografía

- Patterson and Hennessy: Computer Organization and Design. The Hardware/Software Interface. Morgan Kaufmann Publishers. ISBN 1-55860-604-1

Este libro trata de diseño de computadoras en general y de tipo RISC en particular, con ejemplos sacados de la arquitectura MIPS.

- Dominic Sweetman: See MIPS Run. Morgan Kaufmann Publishers. ISBN 1-55860-410-3

El libro definitivo sobre la arquitectura MIPS. Trata la arquitectura de hardware y también habla del software que corre sobre MIPS, como por ejemplo de compiladores y sistemas operativos.

Programación y emulación en MIPS

Hay un simulador gratuito de MIPS R2000/R3000 llamado SPIM para varios sistemas operativos (más concretamente UNIX o GNU/Linux; Mac OS X; MS Windows 95, 98, NT, 2000, XP; y DOS), excelente para aprender el lenguaje ensamblador de los MIPS y de los procesadores RISC en general. http://www.cs.wisc.edu/~larus/spim.html

Existe además un proyecto realizado por alumnos y profesores del DES (Departamento de Electrónica y Sistemas) de la Universidade da Coruña, Simula3MS, que trata de un simulador escrito en Java que permite simular un procesador monociclo, multiciclo o segmentando (únicamente técnicas de segmentación básicas más salto retardado) y maneja el repertorio de instrucciones del MIPS R2000/R3000 (no por completo, aún se encuentra en desarrollo). Tiene algunas características interesantes como por ejemplo, mostrar el camino de datos del procesador simulado, los diagramas multiciclo, etc. La página web es http://simula3ms.des.udc.es

Un emulador de MIPS con más características es el proyecto GXemul (antes conocido como mips64emul), que emula MIPS más avanzados (desde el R4000 hasta el R10000), pero que también emula computadoras completas usando esos microprocesadores. Por ejemplo, GXemul puede emular una DECstation con una CPU MIPS R4400, y una SGI O2 con un MIPS R10000 (aunque la capacidad de correr Irix es bastante limitada), entre otras, además de los framebuffers, controladores SCSI, y elementos típicos de esos sistemas.

Resumen del juego de instrucciones del R3000

Todas las instrucciones del MIPS R3000 son de 32 bits y se dividen en tres tipos de formato: R, I y J.

- Formato R: consta de seis campos, el código de operación (de 6 bits y común a todos los formatos), RS (5 bits, registro fuente, de sólo lectura), RT (5 bits, segundo registro fuente), RD (5 bits, registro destino), Shamt (5 bits, shift amount) y por último el código de función (6 bits).

- Formato I: consta de cuatro campos, los tres primeros son comunes al formato de tipo R (código de operación, RS y RT) y el último campo corresponde a una dirección y consta de 16 bits. El campo dirección puede ser interpretado como un valor inmediato (instrucciones addi, subi, slti,...) o ser un dato clave para calcular direcciones de salto (instrucciones bne, beq,...).

- Formato J: consta de dos campos, el código de operación y un campo de dirección de 26 bits que es utilizado para un modo de direccionamiento pseudo-directo.

Algunas operaciones aritméticas típicas:

- add $1,$2,$3; $1 = $2 + $3 (con signo)

- addu $1,$2,$3; $1 = $2 + $3 (sin signo)

- sub $1,$2,$3; $1 = $2 - $3 (con signo)

- subu $1,$2,$3; $1 = $2 - $3 (sin signo)

- addi $1,$2,100; $1 = $2 + 100 (inmediato)

Algunas instrucciones de E/S con memoria:

- lw $1,100($2); carga una palabra desde la memoria en la posición $2 + 100 en el registro $1.

- sw $1,100($2); graba la palabra que está en el registro $1 en la posición de memoria $2 + 100.

Aquí hay ejemplos de instrucciones de salto y decisión:

- beq $1,$2,100; if ($1 == $2) go to PC+4+100

- slt $1,$2,$3; if ($2 < $3) $1 = 1; else $1 = 0

- j 10000; goto 10000

- jal 10000; $31 = PC and go to 10000

- jr $ra; PC = $ra, o lo que es lo mismo PC = $31

Otras instrucciones importantes:

- lui $1,100; cargar el inmediato en los 16 bits más significativos.

Enlaces externos

Categorías: Wikipedia:Fusionar | Arquitectura de computadoras

Wikimedia foundation. 2010.