- Lógica programada

-

Logica programada es lo contrario de la lógica cableada, es decir, este tipo de diseño permite utilizar un circuito o un proyecto para muchas otras funciones con el simple cambio del software que incorpora.

La lógica programada se basa en dispositivos lógicos programables (PLD), los cuales tienen una función no establecida, al contrario que las puertas lógicas que tienen una función fíja en el momento de su fabricación. Antes de poder utilizar el PLD en un circuito, este debe ser programado.

Contenido

El uso de ROMs como PLDs

Antes de que se inventasen las PLDs, los chips de memoria de solo lectura (ROM) se utilizaban para crear funciones de lógica combinacional arbitrarias con un número determinado de entradas. Considerando una ROM con m entradas, a las que se denomina líneas de dirección; y con n salidas, a las que se denomina líneas de datos. Cuando se utiliza como memoria, la ROM contiene 2m palabras de n bits. Supongamos que las entradas no son direccionadas por una dirección de m-bits, sino por m señales lógicas independientes. Teóricamente, hay 2m funciones booleanas posibles de estas m señales, pero la estructura de la ROM permite solo producir n de estas funciones en los pines de salida. Por lo tanto, en este caso, la ROM se vuelve un equivalente de n circuitos lógicos separados, cada uno generando una función elegida de las m entradas.

La ventaja de utilizar una ROM de esta forma es que cualquier función concebible de las m entradas puede ser colocada por las n salidas, haciendo este el dispositivo lógico combinacional de mayor propósito general disponible. También las PROMs (ROMs programables), EPROMs (PROMs de borrado por ultravioleta) y EEPROMs (PROMs de borrado eléctrico) disponibles pueden ser programadas de esta manera con un programador PROM hardware o software. Sin embargo, existen varias desventajas:

- Son bastante más lentas que los circuitos lógicos dedicados.

- No necesariamente pueden proveer de "protección" ante transiciones lógicas asíncronas.

- Consumen mayor potencia.

- Sólo se utiliza una pequeña fracción de su capacidad en una sola aplicación: un uso ineficiente del espacio.

- Por si solas no pueden ser utilizadas para circuitos de lógica secuencial, puesto que no contienen biestables. Para realizar algunos circuitos secuenciales (como máquinas de estado) se utilizaba un registro TTL externo.

Las EPROMs comunes (como la 2716), se siguen utilizando a veces de esta forma por gente que tiene como hobby el diseño de circuitos, ya que a menudo tienen algunas sueltas. A las ROM utilizadas de esta manera se las conoce como la "PAL del pobre".

Lógica programable temprana

En 1970, Texas Instruments desarrolló un CI de máscara programable basado en la memoria asociativa de sólo lectura (ROAM) de IBM. Este dispositivo, el TMS2000, era programado alterando la capa metálica durante la producción del CI. El TMS2000 tenía hasta 17 entradas y 18 salidas con 8 biestables JK como memoria. Texas Instruments acuño el término Programmable logic array para este dispositivo.

En 1973 National Semiconductor introdujo un dispositivo PLA de máscara programable (DM7575) con 14 entradas y 8 salidas sin registros de memoria. Este era más popular que el de Texas Instruments, pero el coste de hacer la máscara metálica limitaba su uso. El dispositivo es significativo por ser la base de la FPGA (Field Programmable Logic Array) producido por Signetics en 1975, el 82S100.

En 1971, General Electric desarrollaba un PLD basado en la nueva tecnología PROM. Este dispositivo experimental mejoró el ROAM de IBM permitiéndole realizar lógica multinivel. Intel acababa de introducir la PROM de puerta flotante borrable por UV por lo que los desarrolladores en General Electric incorporaron esa tecnología. El dispositivo de General Electric era el primer PLD jamás desarrollado, antecesora del EPLD de Altera en una década. General Electric obtuvo varias patentes tempranas en PLDs.

En 1974, General Electric firmó un acuerdo con Monolithic Memories para desarrollar un PLD de máscara programable incorporando las innovaciones de General. El dispositivo se bautizó como Programmable Associative Logic Array (PALA, matriz lógica asociativa programable). El MMI 5760 fue terminado en 1976 y podía implementar circuitos multinivel o secuenciales de más de 100 puertas. El dispositivo estaba soportado por el entorno de desarrollo de General, donde las ecuaciones Booleanas podían ser convertidas a patrones de máscara para configurar el dispositivo. El integrado nunca se comercializó (hasta ahora debido a lo antes comentado).

PAL

MMI introdujo un dispositivo revolucionario en 1978, la Programmable Array Logic (Matriz lógica programable). La arquitectura era más sencilla que la FPLA de Signetics porque omitía la matriz OR programable. Esto hizo los dispositivos más rápidos, más pequeños y más baratos. Estaban disponibles en encapsulados de 20 pines y DIP de 300 milésimas de pulgada, mientras que las FPLAs venían en encapsulados de 28 pines y DIP de 600 milésimas de pulgada. Ciertas publicaciones sobre PALs desmitificaban el proceso de diseño. El software de diseño PALASM (PAL Assembler, ensamblador PAL) convertía las ecuaciones Booleanas de los ingenieros en el patrón de fusibles requerido para programar el dispositivo. Los PAL de MMI pronto fueron distribuidos por National Semiconductor, Texas Instruments y AMD.

Tras el éxito de MMI con los PAL de 20 pines, AMD introdujo los 22V10 de 24 pines con características adicionales. Tras comprar a MMI (1987), AMD desarrolló una operación consolidada como Vantis, adquirida por Lattice Semiconductor en 1999.

También hay PLAs : Programmable Logic Array.

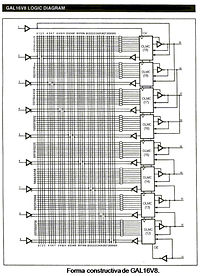

GALs

Una innovación del PAL fue la matriz lógica genérica (Generic array logic) o GAL. Ambas fueron desarrolladas por Lattice Semiconductor en 1985. Este dispositivo tiene las mismas propiedades lógicas que el PAL, pero puede ser borrado y reprogramado. La GAL es muy útil en la fase de prototipado de un diseño, cuando un fallo en la lógica puede ser corregido por reprogramación. Las GALs se programan y reprograman utilizando un programador OPAL, o utilizando la técnica de programación circuital en chips secundarios.

Un dispositivo similar llamado PEEL (programmable electrically erasable logic o lógica programable eléctricamente borrable) fue introducido por la International CMOS

Funcionamiento del GAL

Una GAL permite implementar cualquier expresión en suma de productos con un número de variables definidas, por ejemplo este diagrama muestra la estructura básica de una GAL para dos variables de entrada y una salida. El proceso de programación consiste en activar o desactivar cada celda E2CMOS con el objetivo de aplicar la combinación adecuada de variables a cada compuerta AND y obtener la suma de productos.

Las celdas E2CMOS activadas conectan las variables deseadas o sus complementos con las apropiadas entradas de las puertas AND. Las celdas E2CMOS están desactivadas cuando una variable o su complemento no se utiliza en un determinado producto. La salida final de la puerta OR es una suma de productos. Cada fila está conectada a la entrada de una puerta AND, y cada columna a una variable de entrada o a su complemento. Mediante la programación se activa o desactiva cada celda E2CMOS, y se puede aplicar cualquier combinación de variables de entrada, o sus complementos, a una puerta AND para generar cualquier operación producto que se desee. Una celda activada conecta de forma efectiva su correspondiente fila y columna, y una celda desactivada desconecta la fila y la columna.

Las celdas se pueden borrar y reprogramar eléctricamente. Una celda E2CMOS típica puede mantener el estado en que se ha programado durante 20 años o más. Las macroceldas lógicas de salida (OLMCs) están formadas por circuitos lógicos que se pueden programar como lógica combinacional o como lógica secuencial. Las OLMCs proporcionan mucha más flexibilidad que la lógica de salida fija de una PAL.CPLDs

Las PALs y GALs están disponibles sólo en tamaños pequeños, equivalentes a unos pocos cientos de puertas lógicas. Para circuitos lógicos mayores, se pueden utilizar PLDs complejos o CPLDs. Estos contienen el equivalente a varias PAL enlazadas por interconexiones programables, todo ello en el mismo circuito integrado. Las CPLDs pueden reemplazar miles, o incluso cientos de miles de puertas lógicas.

Algunas CPLDs se programan utilizando un programador PAL, pero este método no es manejable para dispositivos con cientos de pines. Un segundo método de programación es soldar el dispositivo en su circuito impreso. Las CPLDs contienen un circuito que descodifica la entrada de datos y configura la CPLD para realizar su función lógica específica.

Cada fabricante tiene un nombre propietario para este sistema de programación. Por ejemplo, Lattice Semiconductor la llama In-system programming (Programación en el sistema). Sin embargo, estos sistemas propietarios están dejando paso al estándar del Joint Test Action Group (JTAG).

FPGAs

Mientras el desarrollo de las PALs se enfocaba hacia las GALs y CPLDs (ver secciones superiores), apareció una corriente de desarrollo distinta. Esta corriente de desarrollo desembocó en un dispositivo basado en la tecnología de matriz de puertas y se le denominó field-programmable gate array (FPGA). Algunos ejemplos de las primeras FPGAs son la matriz 82s100 y el secuenciador 82S105 de Signetics, presentados a finales de los 70. El 82S100 era una matriz de términos AND, y también tenía funciones de biestable.

Las FPGAs utilizan una rejilla de puertas lógicas, similar a la de una matriz de puertas ordinarias, pero la programación en este caso la realiza el cliente, no el fabricante. El término field-programmable (literamente programable en el campo) se refiere a que la matriz se define fuera de la fábrica, o "en el campo".

Las FPGAs se programan normalmente tras ser soldadas en la placa, en una forma similar a los CPLDs grandes. En las FPGAs más grandes, la configuración es volátil y debe ser reescrita cada vez que se enciende o se necesita una funcionalidad diferente. La configuración se guarda normalmente en una PROM o EEPROM. Las versiones EEPROM pueden ser programadas mediante técnicas como el uso de cables JTAG.

Las FPGAs y los CPLDs son buenas opciones para una misma tarea. Algunas veces la decisión sobre una u otra es más económica que técnica, o puede depender de la preferencia personal o experiencia del ingeniero.

Otras variantes

Actualmente, existe bastante interés en sistemas reconfigurables. Estos sistemas se basan en circuitos microprocesadores y contiene algunas funciones prefijadas y otras que pueden ser alteradas por código en el procesador. Para diseñar sistemas que se auto-alteren, es necesario que los ingenieros aprendan nuevos métodos y que nuevas herramientas de software se desarrollen.

Las PLDs que se venden actualmente, contienen un microprocesador con una función prefijada (el núcleo) rodeado con dispositivos de lógica programable. Estos dispositivos permiten a los diseñadores concentrarse en añadir nuevas características a los diseños sin tener que preocuparse de hacer que funcione el microprocesador.

Almacenamiento de la configuración en las PLDs

Una PLD es una combinación de un dispositivo lógico y una memoria. La memoria se utiliza para almacenar el patrón el que se le ha dado al chip durante la programación. La mayoría de los métodos para almacenar datos en un circuito integrado han sido adaptados para el uso en PLDs. Entre estos se incluyen:

- antifusibles de silicio.

- SRAMs.

- Células EPROM o EEPROM.

- Memoria flash.

Los antifusibles de silicio son elementos de almacenamiento utilizados en las PAL, el primer tipo de PLD. Estos antifusibles se encargan de formar conexiones mediante la aplicación de voltaje en un área modificada del chip. Se le llama antifusibles porque funcionan de manera opuesta a los fusiles normales, los cuales permiten la conexión hasta que se rompen por exceso de corriente eléctrica.

Las SRAM, o RAM estáticas, son un tipo volátil de memoria, lo que quiere decir que su contenido se pierde cada vez que se desconectan. Las PLDs basadas en SRAM tíenen que ser programadas cada vez que el circuito se enciende. Generalmente esto lo hace otra parte del circuito.

Una célula EPROM es un transistor MOS (metal-óxido-semiconductor) que puede activarse atrapando una carga eléctrica permanentemente en su puerta, cosa que realiza un programador PAL. La carga permanece durante algunos años sólo puede ser eliminada exponiendo al chip a una luz ultravioleta fuerte en un dispositivo llamado borrador EPROM.

Las memorias flash son no volátiles, por lo que retienen sus contenidos incluso cuando se les corta la alimentación. Puede ser borradas y reprogramadas tanto como sea necesario, lo que las hace útiles para las memorias PLD.

A partir de 2005, la mayoría de las CPLDs son del tipo EEPROM y no volátiles. Esto se debe a que son demasiado pequeñas para justificar lo poco conveniente que es la programación interna de celdas SRAM cada vez que se inician, y lo costoso de las células EPROM debido a su encapsulado cerámico con una ventana de cuarzo.

Lenguajes de programación de PLDs

Varios dispositivos de programación de PALs admiten la entrada mediante un formato estándar de archivo, denominados comúnmente como 'archivos JEDEC'. Son análogos a los compiladores software. Los lenguajes utilizados como código fuente para compiladores lógicos se denominan lenguajes de descripción de hardware (HDLs).

PALASM y ABEL se utilizan frecuentemente para dispositivos de baja complejidad, mientras que Verilog y VHDL son lenguajes de descripción de hardware de alto nivel muy populares para dispositivos más complejos.

El más limitado ABEL se usa normalmente por razones históricas, pero para nuevos diseños es más popular VHDL, incluso para diseños de baja complejidad.

Véase también

- CPLD

- Matriz de macrocélulas

- Matríz de lógica programable (PAL)

- Field-programmable gate array (FPGA)

- Circuito integrado de aplicación específica (ASIC)

Referencias

- Jorge (25 de febrero del 2009). «Dispositivos Logicos Programables (parte 1)». Consultado el 5 de marzo de 2011.

- Este artículo fue creado a partir de la traducción del artículo Programmable logic device de la Wikipedia en inglés, bajo licencia Creative Commons Atribución Compartir Igual 3.0 y GFDL.

Categorías:- Circuitos digitales

- Componentes activos

Wikimedia foundation. 2010.